來源:內容來自工商時報,謝謝。

在鼓勵員工休假風波後,全球半導體龍頭大廠台積電承諾將持續投資台灣。繼竹科2納米廠之後,據了解,台積電將啓動先導計劃,預計最新2納米以下(1納米)制程擬落腳新竹科學園區轄下的桃園龍潭園區,這也代表國科會明年將展开龍潭園區三期園區報編程序,擴大北部半導體聚落。

全球景氣趨緩、經濟下行風險讓科技大廠一舉一動被放大檢視,台積電日前因鼓勵員工正常休假而受到關注,深夜發聲明強調營運正常,且2023年仍會是成長的一年,同時允諾將持續投資台灣。去年竹科寶山二期擴建案通過環評之後,台積電2納米廠今年第三季已展开整地工作,下一世代設廠位址成爲矚目焦點。

據科技人士透露,台積電下一個先進制程據點,確定將落腳在竹科園區的桃園龍潭基地,由於台積電在龍科已有2個先進封測廠,再加上竹科的地緣、人才支援,「這是最好的位置」。其實,台積電早在2019年時就傳出曾評估過將晶圓制造廠設在龍潭園區新用地,但後續因不明原因而暫時擱置,之後更有二納米以下先進制程重回中科設廠等業界傳言。

竹科轄下的龍潭園區基地現有從業員工數約7,000人,整體年營業額超過500億元,進駐事業主要爲積體電路、光電與生技產業等,已有包括台積電、合晶科技、美商蘋果台灣分公司等產業進駐,今年3月超能高新材料公司新廠才剛動土,讓整個科技產業聚落完整。園區近期因台商回台投資土地需求大增,若台積電要再回到桃園龍潭園區,勢必要再啓動龍潭園區三期开發計畫。

對此,竹科管理局長王永壯表示,關於個別廠商布局情況,在廠商宣布之前不便透露,但單純以龍潭園區來說,第一期事業專用區用地已差不多滿了,第二期主要規劃爲公園、綠地开放空間,未來若有新廠想要進駐、設廠,確實要展开第三期基地評估規劃工作。

台積電未來若要將2納米以下先進制程晶圓廠進駐龍潭,水電需求是否滿足?經濟部官員表示,不便針對單一企業評論,但廠商若有設廠等投資需求,都會與經濟部聯系,盤點水電等需求。若5年後,龍潭園區第三期基地开發完畢、後續有更多新廠商進駐時,水電是否仍然無虞?官員強調,屆時新竹海淡水廠機制已建置完備、桃園用水不再「南供」,加上大潭電廠三個燃氣新機組上线,供水、供電屆時都應沒有問題。

台積電1nm,如何實現?

半導體研發再突破!中國台灣大學、台積電與麻省理工學院(MIT)共同發表研究,首度提出利用「半金屬鉍」(Bi)作爲二維材料的接觸電極,可大幅降低電阻並提高電流,使其效能幾與硅一致,有助實現未來半導體1納米的挑战。這項研究已於《Nature》 期刊公开發表。

台大今(14日)指出,目前硅基半導體主流制程,已進展至五納米及三納米節點,芯片單位面積能容納的電晶體數目,也將逼近半導體主流材料「硅」的物理極限,芯片效能無法再逐年顯著提升。一直以來科學界對二維材料寄予厚望,卻苦於無法解決二維材料高電阻、及低電流等問題,以至於取代硅成爲新興半導體材料一事,始終是「只聞樓梯響」。

此次由台大、台積電與麻省理工學院(MIT)共同發表的研究,首先由美國麻省理工團隊發現在二維材料上搭配半金屬鉍(Bi)的電極,能大幅降低電阻並提高傳輸電流。隨後台積電技術研究部門(Corporate Research)將鉍(Bi)沉積制程進行優化,台大團隊並運用氦離子束微影系統(Helium-ion beam lithography)將元件通道成功縮小至納米尺寸,終於獲得這項突破性的研究成果。

台大電機系暨光電所吳志毅教授進一步說明,使用鉍爲接觸電極的關鍵結構後,二維材料電晶體的效能不但與硅基半導體相當,又有潛力與目前主流的硅基制程技術相容,有助於未來突破摩爾定律的極限。雖然目前還處於研究階段,但該成果能替下世代芯片提供省電、高速等絕佳條件,未來可望投入人工智能、電動車、疾病預測等新興科技的應用。

這項合作自2019年展开,合作時間長達一年半,包括台大、台積電、麻省理工學院等皆投入研究人力。

台大與台積電之間的合作緣份,早自2013年开始,由科技部支持組成產學大聯盟,投入半導體前瞻技術研發,其中第一期計劃(2013年至2017年)累計81項專利申請(70件已獲證);2018年起執行第二期「超3納米前瞻半導體技術研究」計劃,研發成果專利申請有39件。

台積電技術研究組織副處長暨台積電-中國台灣大學聯合研發中心副主任林春榮表示,科學研究能夠驅動產業發展,台積公司多年來致力研發、推動創新,並持續與全球知名大學合作。此次的研究成果再次體現了產學合作的重要性。

1nm後的晶體管,imec將CFET納入路线圖

在 VLSI 2021 上,imec 推出了 forksheet 器件架構,以將納米片晶體管系列的可擴展性擴展到 1nm 甚至更領先的邏輯節點。在forksheet器件中,由於減小了 n 型和 p 型晶體管之間的間距,因此可以使有效溝道寬度大於傳統的環柵納米片器件。這有利於晶體管的驅動電流(或直流性能)。此外,更小的n-to-p間距可以進一步降低標准單元高度,逐步將標准單元推向4T軌道高度設計,這意味着4條單元內金屬线適合標准單元高度範圍。

但是對於 4T cell設計和 16nm 的金屬間距,即使叉板變得太窄,也難以提供所需的性能。P. Schuddinck 等人在 2022 年 VLSI 論文中強調了這一挑战。這就是互補 FET 或 CFET 可以提供緩解的地方。因爲在 CFET 架構中,n 和 pMOS 器件相互堆疊,從而進一步最大化有效溝道寬度。

Julien Ryckaert:“在 CFET 架構中,n 型和 pMOS 器件相互堆疊。堆疊從單元高度考慮中消除了 np 間距,允許進一步最大化有效溝道寬度,從而進一步最大化驅動電流。我們還可以使用由此產生的面積增益將軌道高度推至 4T 及以下。”

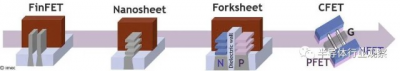

圖1.從 FinFET 到 nanosheet 到 forksheet,最後到 CFET。

兩種不同的實現方案:monolithic和 sequential

研究人員正在探索兩種可能的集成方案,以實現具有挑战性的 nMOS-pMOS 垂直堆疊:單片(monolithic)與順序(sequential)。

單片 CFET 流程從底部通道的外延生長开始,然後是中間犧牲層(sacrificial layer)的沉積,然後是頂部溝道的外延生長。Naoto Horiguchi表示:“雖然這似乎是構建 CFET 最直接的方法,但處理流程相當復雜。例如,堆疊方法產生了非常高的縱橫比垂直結構,這爲進一步圖案化鰭、柵極、間隔物和源極/漏極觸點帶來了關鍵挑战。”

或者,可以使用由幾個塊組成的順序制造流程來制造 CFET。

首先,底層設備被處理到contacts。接下來,使用晶圓對晶圓鍵合技術,通過晶圓轉移在該層的頂部創建一個覆蓋半導體層。然後,集成頂層器件,連接頂柵和底柵。Julien Ryckaert說:“從集成的角度來看,這個流程比單片流程更簡單,因爲底層和頂層設備都可以以傳統的‘二維’方式單獨處理。此外,它還提供了爲 n 型和 p 型器件集成不同溝道材料的獨特可能性。”

PPAC 基准測試:(優化的)順序 CFET 是單片 CFET 的有效替代方案

在P. Schuddinck 等人在 2022 年發表的 VLSI 論文中,作者提出了 4T 標准單元設計中單片 CFET 與順序 CFET 的 PPAC 評估 。

Julien Ryckaert說:“從這個基准來看,使用單片工藝流程制造的 CFET 消耗更少的面積,並且優於其有效電容增加的連續對應物。然而,我們表明,通過應用三個優化,我們可以將順序 CFET 的軌跡與單片 CFET 的軌跡相提並論:(1)自對准柵極合並(圖中的(v2)),(2)省略柵極cap (v3) 和 (3) 使用混合定向技術,稱爲 HOT。”

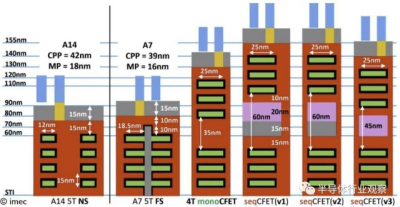

圖2.nansoheet (NS)、forksheet (FS) 和 CFET(單片和順序)的柵極橫截面。基本順序 CFET (=v1) 比單片設計更寬、更高。通過優化流程(包括自對准柵極合並 (v2) 和無柵極帽 (v3)),順序 CFET 在面積消耗方面接近單片 CFET(也在 VLSI 2022 上介紹)。

HOT 允許獨立優化頂部和底部器件的晶體取向和應變工程,而不會增加工藝流程成本。例如,在 n-on-p 配置中,可以在頂部使用具有 取向的硅片,從而爲頂部 nMOS 器件提供最高的電子遷移率。而對於底部,pMOS 空穴遷移率受益於 硅片取向。Julien Ryckaert:“盡管單片 CFET 仍然是首選,但順序工藝流程的獨特之處在於它可以利用晶圓方向的這種差異。

通過這些優化,我們的基准測試表明,對於未來 4T 軌道設計,順序 CFET 流程可以成爲更復雜的單片 CFET 的有效替代方案。”

逐步改進模塊和集成步驟

近年來,imec 報告了在改進單片和順序 CFET 的模塊和集成步驟方面取得的進展。

例如,在 VLSI 2020 上,imec 率先展示了通過優化關鍵模塊步驟實現的單片集成 CFET 架構 。

對於順序 CFET,也報告了逐步改進。盡管底層和頂層器件可以以傳統的“二維”方式分开處理,但晶圓轉移帶來了特定的挑战。例如,它對層轉移和頂層設備處理都具有熱預算限制(大約 500C 或以下),以避免對底層設備產生任何負面影響。這是頂層器件的柵極堆疊可靠性的一個問題,它通常需要 900C 量級的熱步驟。

早些時候,imec 展示了保持良好柵極堆疊可靠性的新方法,其中包括對 pMOS 頂部器件進行低溫氫等離子體處理。

優化的低溫 Smart Cut TM層轉移工藝——順序 CFET 的關鍵構建模塊

在 A. Vandooren 等人在 2022 年發表的 VLSI 論文中,imec 評估了三種不同的層轉移過程 。在本文中,作者研究了各種工藝選項對頂部(完全耗盡的絕緣體上硅 (FD-SOI))和底部(體 FinFET)器件的器件性能的影響。

Naoto Horiguchi說:“從成本的角度來看,特別有前途的是 SOITEC 的低溫 Smart Cut TM流程,它使用工程化的體施主晶圓來實現低溫下的薄層分裂。這種方法的美妙之處在於它允許重復使用供體晶圓,使其成爲一種具有成本效益的解決方案。其他兩種方法都依賴於通過研磨和硅回蝕去除襯底,這不允許重新使用供體晶圓。”

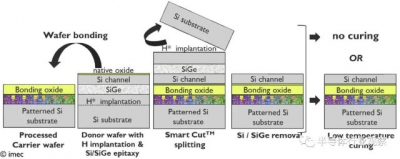

圖3.SOITEC 低溫 Smart Cut TM層轉移流程的描述,無固化或低溫固化(也在 2022 VLSI 上展示)。

通過進一步優化,在使用低溫 Smart Cut 進行概念驗證層轉移後處理的頂級器件顯示可以從降低的電氣性能中恢復。Naoto Horiguchi表示:“由於未經優化的低溫固化,這些設備的電子遷移率較低。Soitec 進一步开發了其解決方案,表明我們可以通過優化低溫固化步驟來恢復遷移率損失,從而提高 Si 通道的晶體質量。鑑於這種方法的成本效益,我們認爲具有新开發工藝條件的 Smart Cut TM是在順序 CFET 工藝流程中執行層轉移的有效選擇。

它提供了一個通用流程,支持 CFET 之外的 3D 順序堆疊應用,例如 memory-on-logic 或 logic-on-logic 的 3D 順序集成。”

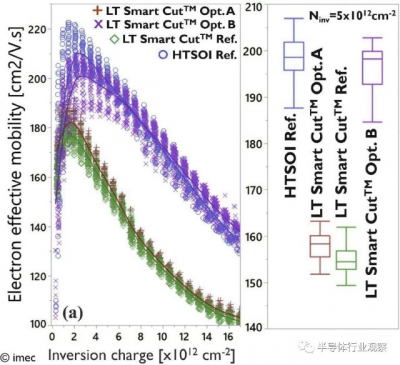

圖 4 - 低溫 Smart Cut TM層轉移方法的電子有效場遷移率與反轉電荷,比較優化和參考(概念驗證)工藝條件。該圖顯示了 Opt 改進的移動性。B(紫色),表示額外的低溫固化步驟(也在 VLSI 2022 上介紹)。

通過這些測試設備,作者還展示了頂部和底部設備之間良好的電氣互連性,並通過功能逆變器鏈進行了驗證。此外,如上所述,通過集成氫等離子體處理步驟,可以保持頂層 pMOS 器件的柵極堆疊可靠性。

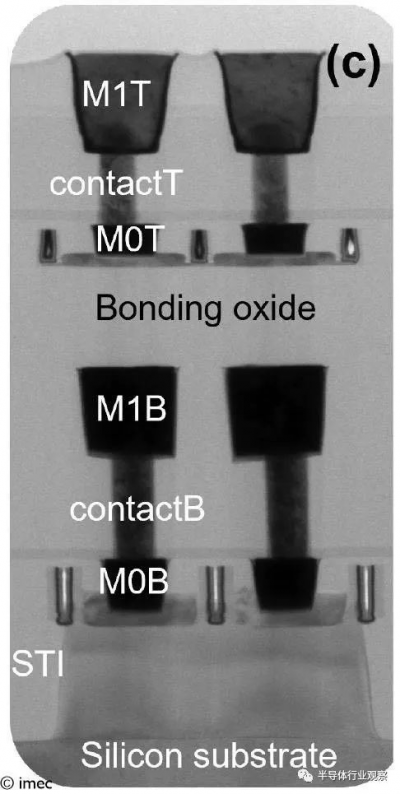

圖5.3D 順序堆疊器件的 TEM 橫截面(也在 VLSI 2022 上展示)。

“我想強調的是,這種架構還不是真正的 CFET 實現,”Naoto Horiguchi 補充道。“例如,在設想的順序 CFET 架構中,底部器件的金屬互連層 (M1B) 不存在。A. Vandooren 的 VLSI 論文中展示了我們的測試工具,用於演示改進的層轉移作爲順序 CFET 和其他 3D 順序堆疊實現的關鍵模塊。

未來,IMEC 表示,將繼續努力優化集成步驟,最終將展示真正的順序 CFET 實施。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電1nm最新消息,2027年量產?

地址:https://www.breakthing.com/post/26734.html