來源:內容由半導體行業觀察編譯自Venturebeat,謝謝。

英特爾宣布其研究人員預見到一種通過改進封裝和厚度僅爲三個原子的材料層使芯片密度提高 10 倍的方法。這可能爲到 2030 年在芯片封裝上放置一萬億個晶體管鋪平道路。

英特爾展示了可以使摩爾定律走上正軌的進步。(圖片來源:英特爾)

摩爾定律應該已經死了。芯片不應該變得更好,至少不會通過傳統的制造進步。在晶體管發明 75 周年之際,這是一個令人沮喪的想法。早在 1965 年,英特爾名譽董事長戈登摩爾就預測,芯片上的元件或晶體管數量每隔幾年就會翻一番。

該法律持續了幾十年。芯片變得更快、更高效。芯片制造商縮小了芯片的尺寸,結果是好的。微型芯片中的電子行進距離更短。所以芯片變得更快了。更短的距離意味着芯片使用的材料更少,從而使其更便宜。因此,摩爾定律的穩步推進意味着芯片可以同時變得更快、更便宜,甚至更省電。

但摩爾定律確實依賴於傑出的人類工程師提出更好的芯片設計和持續的制造小型化。近年來,取得這些進展變得越來越困難。芯片設計符合物理定律。有了幾個原子厚的原子層,就不可能再收縮了。因此,英偉達首席執行官黃仁勳最近表示,“摩爾定律已死。”

英特爾展示了它如何制造具有復雜互連封裝的芯片。

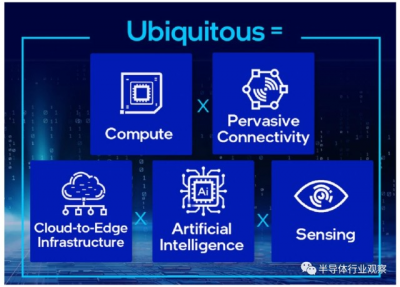

這不是個好時機,因爲我們正要开始構建元宇宙。摩爾定律對於滿足世界永無止境的計算需求至關重要,因爲激增的數據消費和對人工智能 (AI) 增長的推動帶來了有史以來最大的需求加速。

在 Nvidia 首席執行官發表上述言論一周後,英特爾首席執行官帕特基辛格 (Pat Gelsinger) 表示,摩爾定律仍然有效。這並不奇怪,因爲他已經在美國的新芯片制造廠投資了數百億美元。不過,他的研究人員在國際電子設備會議上支持他。英特爾明確表示,這些進步可能需要五到十年的時間。

在研究活動的論文中,英特爾描述了在未來十年內將摩爾定律保持在封裝上一萬億個晶體管的軌道上的突破。英特爾元器件研究總監兼高級首席工程師 Paul Fischer 在新聞發布會上表示,在 IEDM 上,英特爾研究人員展示了 3D 封裝技術的進步,密度提高了 10 倍。

“我們的使命是讓我們的工藝技術選擇更加豐富和完整,”他說。

這些包最近以創新的方式使用;英特爾的競爭對手 Advanced Micro Devices 宣布其最新的圖形芯片有一個處理器芯片和六個內存芯片——所有這些芯片都連接在一個封裝中。英特爾表示,它與政府實體、大學、行業研究人員和芯片設備公司合作。英特爾在 IEDM 活動等場所分享研究成果。

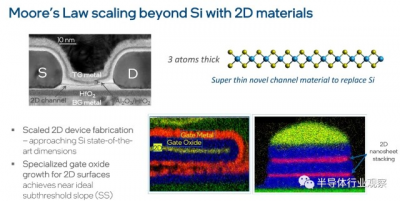

英特爾還推出了超越 RibbonFET 的新型二維晶體管材料,包括只有三個原子厚的超薄材料。它還描述了用於更高性能計算的能源效率和內存的新可能性;和量子計算的進步。

“自晶體管發明 75 年以來,推動摩爾定律的創新繼續滿足世界對計算的呈指數增長的需求,”英特爾組件研究和設計支持副總裁 Gary Patton 在一份聲明中說。“在 IEDM 2022 上,英特爾展示了突破當前和未來障礙所需的前瞻性和具體研究進展,滿足這種永無止境的需求,並在未來幾年保持摩爾定律的活力。”

晶體管迎來75周年生日

芯片電路之間的層厚度可以低至三個原子。

爲紀念晶體管問世 75 周年,英特爾執行副總裁兼技術开發總經理 Ann Kelleher 將主持 IEDM 的全體會議。Kelleher 將概述持續行業創新的前進道路——圍繞基於系統的战略凝聚生態系統,以滿足世界對計算日益增長的需求,並更有效地創新以摩爾定律的步伐前進。

會議主題爲“慶祝晶體管問世 75 周年!看看摩爾定律創新的演變,”於太平洋標准時間 12 月 5 日上午 9:45 舉行。

爲了取得所需的進步,英特爾採取了多管齊下的方法,即“在英特爾內部的影響力越來越大,影響力越來越大”,以跨越多個學科。

Fischer 說,英特爾必須在芯片材料、芯片制造設備、設計和封裝方面取得進展。

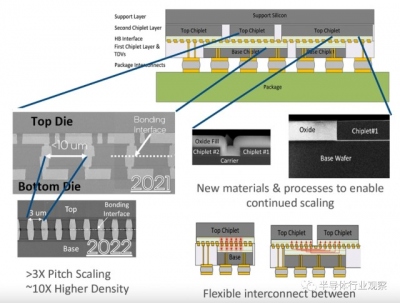

他說:“3D 封裝技術正在實現小芯片的無縫集成,”或封裝中的多個芯片。“我們正在模糊硅結束和封裝开始之間的界限。”

持續創新是摩爾定律的基石。在過去二十年中,個人電腦、圖形處理器和數據中心的許多關鍵創新裏程碑(包括應變硅、Hi-K 金屬柵極和 FinFET)的持續功率、性能和成本改進都始於英特爾的組件研究小組。

進一步的研究,包括 RibbonFET 環柵 (GAA) 晶體管、PowerVia 背面功率傳輸技術以及 EMIB 和 Foveros Direct 等封裝突破,都在今天的路线圖上。

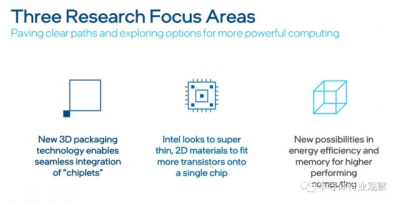

在 IEDM 2022 上,英特爾的組件研究小組表示正在开發新的 3D 混合鍵合封裝技術,以實現小芯片的無縫集成;超薄二維材料,可將更多晶體管裝入單個芯片;以及用於更高性能計算的能源效率和內存的新可能性。

英特爾將如何做?

英特爾預見到對計算能力的巨大需求。

研究人員已經確定了模糊封裝和硅之間界限的新材料和新工藝。英特爾表示,它預計將從今天的芯片上數百億個晶體管發展到一個封裝上的萬億晶體管,其中可以包含很多芯片。

取得進步的一種方法是通過封裝實現額外 10 倍的互連密度,從而形成准單片芯片。英特爾的材料創新還確定了實用的設計選擇,這些選擇可以使用僅三個原子厚的新型材料滿足晶體管縮放的要求,從而使公司能夠繼續擴展到 RibbonFET 之外。

英特爾在 IEDM 2022 上展示的最新混合鍵合研究表明,與英特爾在 IEDM 2021 上的研究展示相比,功率和性能密度又提高了 10 倍。

持續的混合鍵合縮放到三納米間距可實現與單片系統級芯片連接相似的互連密度和帶寬。一納米是十億分之一米。

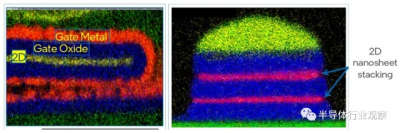

英特爾表示,它正在尋找超薄“2D”材料,以便將更多晶體管安裝到單個芯片上。英特爾展示了一種環柵堆疊納米片結構,它使用只有三個原子厚的薄二維通道,同時在室溫下以低漏電流實現了雙柵結構上晶體管近乎理想的开關。

這是堆疊 GAA 晶體管和超越硅的基本限制所需的兩個關鍵突破。

研究人員還揭示了對二維材料的電接觸拓撲結構的首次綜合分析,這可以進一步爲高性能和可擴展的晶體管通道鋪平道路。

爲了更有效地利用芯片面積,英特爾通過开發可垂直放置在晶體管上方的內存來重新定義縮放比例。英特爾率先展示了堆疊式鐵電電容器,其性能與傳統鐵電溝槽電容器的性能相匹配,可用於在邏輯芯片上構建 FeRAM。

業界首創的器件級模型可捕獲改進的鐵電氧化鉿器件的混合相和缺陷,標志着英特爾在支持行業工具开發新型存儲器和鐵電晶體管方面取得了重大進展。

英特爾通過多種方法找到了通往萬億晶體管芯片的道路。

英特爾正在爲 300 毫米硅基 GaN 晶圓打造一條可行的道路,讓世界離超越 5G 更近一步並解決能效挑战。英特爾在這一領域的突破表明,增益是行業標准 GaN 的 20 倍,並創下了高性能功率傳輸的行業記錄。

英特爾正在超級節能技術方面取得突破,特別是不會忘記的晶體管,即使在電源關閉時也能保留數據。英特爾研究人員已經打破了阻礙該技術在室溫下完全可行和運行的三個障礙中的兩個。

英特爾繼續在物理學中引入新概念,並在爲量子計算提供更好的量子比特方面取得突破。英特爾研究人員致力於通過更好地了解各種可能作爲影響量子數據的環境幹擾的界面缺陷來尋找更好的方法來存儲量子信息。

點擊文末「閱讀原文」,可查看英文鏈接。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:英特爾發現2030年實現萬億晶體管芯片的途徑

地址:https://www.breakthing.com/post/35910.html