通常,我們更喜歡把台式機/筆記本電腦的復雜指令集叫做CISC,把智能手機的精簡指令集叫做RISC。戴爾和蘋果等 OEM 一直在其筆記本電腦中使用 x86 CISC 處理器。讓我在這裏解釋筆記本電腦的設計方法。主板以多核CISC處理器爲主要部件,連接GPU、RAM、存儲內存等子系統和I/O接口。操作系統在多核處理器上並行運行多個應用程序,管理內存分配和 I/O 操作。

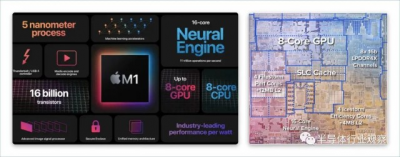

這就是我們使用處理器實現任何電子系統的方式。然而,我們更喜歡使用 RISC 處理器的智能手機系統級芯片,因爲它有助於我們減小主板的尺寸和功耗。幾乎整個具有多核 RISC CPU、GPU、DSP、無线和接口子系統、SRAM、閃存和 IP 的系統都在 SoC 上實現。OEM Apple 正在遵循這款智能手機的 SoC 設計方法,甚至將他們的 MAC 筆記本作爲 OEM 潮流引領者。所有最新的 MAC 書籍都使用他們的 M 系列 SoC,這些 SoC 使用 ARM 的 RISC 處理器。

因此,很明顯,英特爾的 x86 或 ARM 的 RISC 處理器的專有 ISA 一直是 Apple、戴爾、三星等 OEM 的選擇,但現在爲什么我們需要像 RISC-V 這樣的开放 ISA,而不是所有這些經過充分驗證的ISA。

在今天的情況下,每個人都將 SoC 用於他們的筆記本電腦和智能手機。這種復雜的 SoC 需要通用處理器和專用處理器。爲了實現像 Apple 的 M 系列 SoC 這樣的芯片,我們需要不同種類的處理器,如 RISC CPU、GPU、DSP、安全處理器、圖像處理器、機器學習加速器、安全和神經引擎,基於來自多個 IP 的各種通用和專用 ISA供應商,如圖1所示。

圖 1:Apple M1 SoC 參考:AnandTech

在這種情況下,主要挑战是:

1.選擇並與多家 IP 供應商合作

2.不同的 IP 供應商可能有不同的 IP 許可方案,工程師將無法自由地定制 ISA 和設計,因爲他們更愿意滿足他們的設計目標。

3.所有專門的 ISA 都不會持續/生存很長時間,從而影響長期產品支持計劃和路线圖。

4.此外,涉及多個 ISA 和工具鏈的軟件/應用程序开發和更新將具有挑战性。

RISC-V 是一種具有多種擴展功能的通用免許可开放式 ISA。它是一個 ISA,分爲一個小的基本整數 ISA,可用作定制加速器和可選標准擴展的基礎,以支持通用軟件开發。

您可以添加自己的擴展來實現您的專用處理器,或者根據需要自定義基本 ISA,因爲它是开放的。沒有許可證限制。因此,在未來,我們可以僅使用一個 RISC-V ISA 創建所有通用和專用處理器,並實現任何復雜的 SoC。

什么是 RISC-V,它與其他 ISA 有何不同?

RISC-V 是加州大學伯克利分校的第五個主要 ISA 設計。它是由非營利組織 RISC-V International維護的开放式 ISA,涉及所有利益相關者社區以實施和維護 ISA 規範、黃金參考模型和合規性測試套件。

RISC-V 不是 CPU 實現。它是通用處理器和專用處理器的开放式 ISA。一個完全开放的 ISA,可供學術界和工業界免費使用。

RISC-V ISA 被分成一個小的基本整數 ISA,可單獨用作定制加速器或教育目的的基礎,以及支持通用軟件开發的可選標准擴展

RISC-V 支持應用程序、操作系統內核和硬件實現的 32 位和 64 位地址空間變體。因此,它適用於所有計算系統,從嵌入式微控制器到雲服務器,如下所述。

簡單的嵌入式微控制器、保護運行 RTOS 的嵌入式系統、運行操作系統的台式機/筆記本電腦/智能手機以及運行多個操作系統的雲服務器。

二、RISC-V 基礎 ISA

RISC-V 是一個相關 ISA 家族:RV32I、RV32E、RV64I、RV128I。

RV32I/ RV32E/ RV64I/RV128I 是什么意思:

RV——RISC-V

32/64/128 – 定義寄存器寬度 [XLEN] 和地址空間

I – 整數基 ISA

32 個用於所有基本 ISA 的寄存器

E – 嵌入式:只有 16 個寄存器的基本 ISA

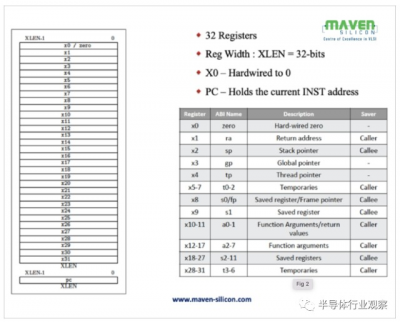

(1)RISC-V 寄存器:

所有基本 ISA 都有 32 個寄存器,如圖 2 所示,除了 RV32E。只有RV32E base ISA對於簡單的嵌入式微控制器只有16個寄存器,但寄存器寬度仍然是32位。

寄存器 X0 硬接线爲零。稱爲程序計數器的特殊寄存器保存要從內存中獲取的當前指令的地址。

如圖 2 所示,RISC-V 應用程序二進制接口,ABI 定義了寄存器的標准功能。爲了簡單和一致,軟件开發工具通常使用 ABI 名稱。根據 ABI,額外的寄存器專用於 X0 到 X15 範圍內的保存寄存器、函數參數和臨時變量,主要用於 RV32E 基礎 ISA,它只需要前 16 個寄存器來實現簡單的嵌入式微控制器。但是 RV32I 基礎 ISA 將擁有所有 32 個寄存器 X0 到 X31。

圖 2:RISC-V 寄存器和 ABI 名稱參考:RISC-V 規範

(2)RISC-V內存:

RISC-V hart [硬件线程/核心] 具有用於所有內存訪問的 2^XLEN 字節的單字節可尋址地址空間。XLEN 表示整數寄存器的位寬度:32/64/128。

內存字定義爲 32 位(4 字節)。相應地,半字爲16位(2字節),雙字爲64位(8字節),四字爲128位(16字節)。

內存地址空間是循環的,因此地址 2^XLEN -1 處的字節與地址零處的字節相鄰。因此,由硬件完成的內存地址計算忽略溢出,而是環繞模 2^XLEN。

RISC-V 基礎 ISA 具有小端或大端存儲系統,特權架構進一步定義了大端操作。指令作爲 16 位小尾數法包的序列存儲在內存中,而不管內存系統的字節順序如何。

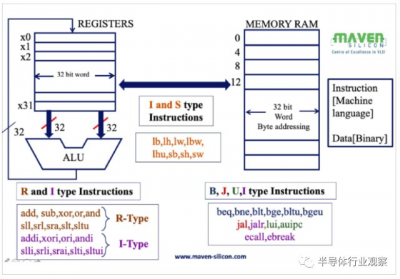

(3)RISC-V 加載存儲架構

您可以可視化基於 RISC-V 寄存器和內存的 RISC-V 加載存儲架構,如下圖 3 所示。

RISC-V處理器根據PC中的地址從主存中取/載指令,譯碼32位指令,然後ALU進行算術/邏輯/內存讀寫操作。ALU 的結果將存儲回其寄存器或內存中。

圖 3:RISC-V 加載存儲架構

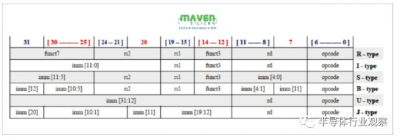

(4)RISC-V RV32 I 基礎 ISA

RV32I base ISA 只有 40 條 Unique Instructions,但簡單的硬件實現只需要 38 條指令。RV32I指令可分爲:

R-Type:注冊到注冊說明

I-Type:立即注冊、加載、JLR、Ecall 和 Ebreak

S型:商店

B型:分支

J型:跳躍和鏈接

U 型:立即加載/添加上層

圖 4:RV32I 基本 ISA 指令格式

(5)用於優化 RTL 設計的 RISC-V ISA

在這裏,我想解釋一下 RISC-V ISA 如何使我們能夠實現優化的寄存器傳輸級設計,以滿足低功耗和高性能的目標。

如圖 4 所示,RISC-V ISA 在所有格式中將源(rs1 和 rs2)和目標(rd)寄存器保持在相同位置以簡化解碼。

立即數總是經過符號擴展,並且通常被打包到指令中最左邊的可用位,並且已被分配以降低硬件復雜性。尤其是,

所有立即數的符號位總是在指令的第 31 位以加速符號擴展電路。

符號擴展是對立即數最關鍵的操作之一(特別是對於 XLEN>32),在 RISC-V 中,所有立即數的符號位始終保存在指令的第 31 位中,以允許符號擴展與指令解碼並行進行。

爲了加快解碼速度,基礎 RISC-V ISA 將最重要的字段放在每條指令的同一位置。正如您在指令格式表中所見,

主要操作碼總是在位 0-6 中。

目標寄存器(如果存在)始終位於位 7-11 中。

第一個源寄存器(如果存在)始終位於第 15-19 位。

第二個源寄存器(如果存在)始終位於第 20-24 位。

但是爲什么立即位會被打亂呢?想想解碼直接場的物理電路。由於它是硬件實現,因此這些位將被並行解碼;輸出立即數中的每一位都有一個多路復用器來選擇它來自哪個輸入位。多路復用器越大,成本越高,速度也越慢。

值得注意的是,只需要主要操作碼(位 0-6)就可以知道如何解碼立即數,因此立即數解碼可以與指令其余部分的解碼並行完成。

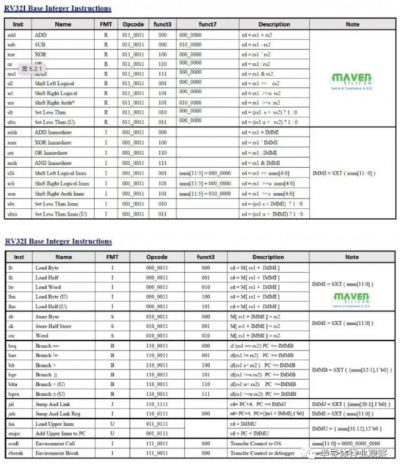

(6)RV32I 基本 ISA 指令

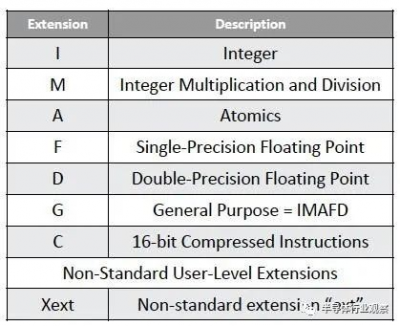

RISC-V ISA 擴展

此處列出了所有 RISC-V ISA 擴展:

圖 5:RISC-V ISA 擴展

我們遵循 RISC-V 處理器的命名約定,如下所述:

RISC-V 處理器:RV32I、RV32IMAC、RV64GC

RV32I:整數基礎 ISA 實現

RV32IMAC:整數基礎 ISA + 擴展:[乘法 + 原子 + 壓縮]

RV64GC:64 位 IMAFDC [G-通用:IMAFD]

整數 64 位基本 ISA + 擴展:[乘法 + 原子 + SP 浮動 + DP 浮動 + 壓縮]

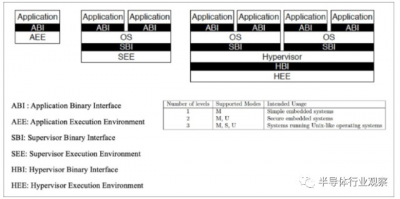

RISC-V 特權架構

RISC-V 特權架構涵蓋了 RISCV 系統的所有方面,超出了我到目前爲止所解釋的非特權 ISA。特權架構包括特權指令以及運行操作系統和連接外部設備所需的附加功能。

根據 RISC-V 特權規範,我們可以實現從簡單的嵌入式控制器到復雜的雲服務器的不同類型的系統,如下所述。

應用程序執行環境 – AEE:“裸機”硬件平台,其中 harts 直接由物理處理器线程實現,指令可以完全訪問物理地址空間。硬件平台定義了一個從上電復位开始的執行環境。示例:簡單且安全的嵌入式微控制器

主管執行環境——參見:RISC-V 操作系統,通過將用戶級 harts 多路復用到可用的物理處理器线程並通過虛擬內存控制對內存的訪問來提供多個用戶級執行環境。

示例:運行類 Unix 操作系統的桌面等系統

Hypervisor Execution Environment – HEE:RISC-V hypervisor,爲來賓操作系統提供多個管理級執行環境。

示例:運行多個guest操作系統的雲服務器

圖 6:RISC-V 特權軟件堆棧參考:RISC-V 規範

此外,RISC-V 特權規範定義了各種控制和狀態寄存器 [CSR],以實現各種功能,如任何系統的中斷、調試和內存管理設施。您可能需要參考規範以探索更多信息。

如本文所述,我們可以使用通用的开放式 RISC-V ISA 高效地實現任何系統,從簡單的物聯網設備到復雜的智能手機和雲服務器。由於單片半導體縮放失敗,專業化是提高計算性能的唯一途徑。开放式 RISC-V ISA 是模塊化的,支持自定義指令,使其成爲創建各種專用處理器和加速器的理想選擇。

隨着 IEEE 標准通用驗證方法論的出現,我們在芯片驗證方面取得了巨大成功,开放的 RISC-V ISA 也將繼承各種專有 ISA 的所有優點,成爲行業標准 ISA,引領我們走向未來开放的計算時代。您准備好使用 RISC-V 專業知識迎接這個美好的未來了嗎?

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:RISC-V給我們帶來了什么?

地址:https://www.breakthing.com/post/36338.html