來源:內容由半導體行業觀察(ID:icbank)編譯自semiwiki,謝謝。

模擬單元設計和遷移的世界與數字單元有很大不同,因爲模擬單元的輸入和輸出通常具有隨時間連續變化的電壓電平,而不僅僅是在 1 和 0 之間切換。台積電的 Kenny Hsieh 就該主題發表了演講在最近的北美OIP 活動中研究模擬cell的遷移,我觀看了他的演講以更多地了解他們應對這些挑战的方法。

模擬單元挑战

從 N7 到 N5 再到 N3,模擬設計規則的數量急劇增加,同時需要考慮更多的布局效果。模擬單元高度往往是不規則的,因此沒有像標准單元那樣的鄰接。附近的晶體管布局會影響相鄰的晶體管性能,需要花費更多時間進行驗證。

台積電從 N5 節點开始的模擬單元的方法是使用具有固定單元高度的布局,支持單元鄰接以形成陣列,重復使用 Metal 0 及以下的預繪制布局,並且經過硅驗證。模擬單元的 PDK 內部是有源單元,加上所有其他參數:CMOS、保護環、CMOS 抽頭、去電容和變容二極管。

模擬單元現在使用固定高度,放置在軌道中,您可以在其中使用基台(abutment),甚至可以自定義transition, tap 和保護區域。模擬單元的所有可能組合都經過詳盡的預驗證。

模擬單元

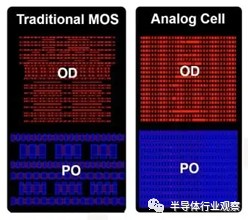

通過這種模擬電池方法,可以實現均勻的氧化物擴散 (OD) 和多晶硅 (PO),從而提高硅良率。

模擬單元布局

66自動化模擬單元布局

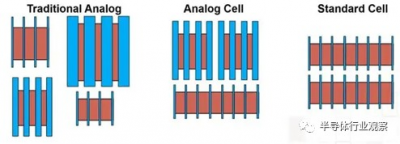

通過限制模擬單元內的模擬晶體管使用更規則的模式,可以更容易地使用布局自動化,例如:使用模板、自動布局、具有電氣感知寬度和空間的自動布线,以及添加備用晶體管以支持任何 ECO在設計過程的後期到達。

模擬單元的常規布局

在節點之間遷移時,原理圖拓撲被重新使用,而每個設備的寬度和長度確實發生了變化。APR 設置針對單元格的每個模擬組件進行調整。電流和寄生匹配等模擬指標的 APR 約束使該過程更加智能。爲了支持 ECO 流程,有一個自動備用晶體管插入功能。自 2021 年以來, Cadence和Synopsys都與台積電合作,以實現這種改進的模擬自動化方法。

將模擬電路遷移到新的工藝節點需要一系列設備映射、電路優化、版圖重用、模擬 APR、EM 和 IR 修復以及版圖後仿真。在映射期間,使用 Id 飽和方法,其中設備由其上下文自動識別。

僞布局後仿真可以使用估計值和一些完全提取的值來縮短分析循環。Cadence 和 Synopsys 對 IC 版圖工具的增強現在支持原理圖遷移、電路優化和版圖遷移步驟。

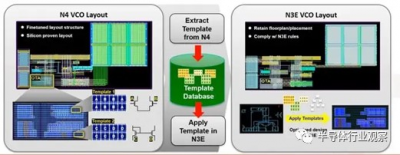

使用自動化步驟和模板方法將 N4 的 VCO 布局遷移到 N3E 節點,重用差分對和電流鏡像設備的布局和方向。將新的自動化遷移方法與手動方法進行比較,其中手動遷移所需時間爲 50 天,而自動化僅需 20 天,因此生產率提高了 2.5 倍。早期的 EM、IR 和寄生 RC 檢查是實現生產力提升的基礎。

N4 到 N3E VCO 布局遷移

基於環的 VCO 也使用 Pcells 從 N40 手動和自動遷移到 N22 節點。通過使用自動化流程,生產率提高了 2 倍。Pcells 有更多的限制,所以生產率的提高有點少。

66總結

台積電通過以下方式面臨模擬單元遷移的挑战:與 Cadence 和 Synopsys 等 EDA 供應商合作修改他們的工具,使用具有固定高度的模擬單元以允許更多布局自動化,以及採用與數字流程類似的策略。兩個遷移示例表明,使用較小的節點(如 N5 到 N3)時,生產率提高可以達到 2.5 倍。即使使用像 N40 這樣的成熟節點,使用 Pcell 也可以預期將生產率提高 2 倍。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電談5nm後的模擬設計

地址:https://www.breakthing.com/post/37711.html