衆所周知,我們生活在一個數字大爆炸的時代,需要處理的數據比以往任何時候都多,存儲器在數據流中起着關鍵作用。存儲技術發展更迭50年,逐漸形成了SRAM、DRAM及Flash這三大主要領域。但是隨着半導體制造技術持續朝更小的技術節點邁進,傳統的DRAM和NAND Flash面臨越來越嚴峻的微縮挑战;再加上由於這些存儲技術與邏輯計算單元之間發展速度的失配,嚴重制約了計算性能和能效的進一步提升。

因此,業界开始對新型存儲技術寄予厚望。越來越多的新型技術迅速湧現,例如將處理任務移到內存附近甚至是內部,分別對應爲近存計算和存內計算,以此來提高效率。他們使用新型的存儲材料和機制來存儲數據。

台積電作爲追逐先進工藝的扛把子,對於新型存儲技術的布局也是緊鑼密鼓,畢竟邏輯和存儲是芯片重要的兩條腿,一個也不能落下。台積電在研的新型存儲器解決方案主要涉及磁阻式隨機存取存儲器(MRAM)、電阻式隨機存取存儲器 (RRAM)、相變隨機存取存儲器 (PCRAM)、鐵電RAM等。台積電近年來積極推動將嵌入式閃存(sFlash)改成MRAM和ReRAM等新型存儲制程。

MRAM

在新興的非易失性二進制存儲器中,自旋轉矩傳遞RAM (STT-MRAM)、自旋軌道轉矩RRAM (SOT MRAM)和壓控MRAM (VC MRAM)因其工作電壓低、速度快和耐用性以及先進的CMOS技術兼容性而特別具有吸引力。

台積電研發STT-MRAM解決方案主要是用來克服嵌入式閃存技術的擴展限制。在2021年IEEE會議上,台積電展示了嵌入16nm FinFET CMOS工藝的STT-MRAM的可靠性和抗磁性。

此外,台積電還在積極探索SOT-MRAM和VC-MRAM,並與外部研究實驗室、財團和學術合作夥伴合作。台積電的SOT-MRAM探索由高速(

RRAM

台積電認爲,AI和IoT所組成的強大組合AIoT,可能會在未來幾年推動半導體行業的增長。高能效機器學習需要具有低功耗的大容量片上存儲器。它可以同時支持 1T1R(1 個晶體管 + 1RRAM)和 1S1R(1 個選擇器 + 1RRAM)陣列架構。與傳統的1T1R架構相比,1S1R架構可以實現更高的密度並實現3D集成。2020年台積電开始生產28nm電阻隨機存取存儲器(RRAM),這是台積電爲價格敏感的物聯網市場所开發的低成本解決方案。

2022年11月25日,英飛凌和台積電宣布,兩家公司准備將台積電的RRAM非易失性存儲器 (NVM) 技術引入英飛凌的下一代AURIX™微控制器 (MCU),首批基於28納米 RRAM 技術的樣品將於2023年底提供給客戶。目前,市場上的大多數 MCU系列都基於嵌入式閃存技術。RRAM的引入對MCU來說是一項新的革新,RRAM NVM可以進一步擴展到 28 納米及以上。台積電和英飛凌成功爲在汽車領域引入RRAM奠定了基礎。

台積電還在繼續探索新的RRAM材料堆棧及其密度驅動集成,以及可變感知電路設計和編程結構,以實現面向AIoT應用的高密度嵌入式RRAM解決方案選項。

PCRAM

相變隨機存儲器(PCRAM)是一種基於硫化物玻璃的非易失性存儲器。通過控制焦耳加熱和淬火,PCRAM在非晶態(高電阻)和晶體態(低電阻)之間過渡的電阻。存儲器的電阻狀態在很大程度上與非晶態區域的大小及其可控性和穩定性有關。這使得PCRAM細胞獨特地能夠存儲多個狀態(電阻),從而具有比傳統二進制存儲器更高的有效細胞密度的潛力。PCRAM可以支持陣列配置,包括一個晶體管和一個存儲器(1T1R)陣列和密度更大的一個選擇器和一個存儲器(1S1R)陣列。

相變存儲器具有很有前途的多級單元 (MLC) 功能,可滿足神經形態和內存計算應用中不斷增長的片上存儲器容量需求。台積電一直在探索PCRAM材料、電池結構和專用電路設計,以實現AI和ML的近內存和內存計算。台積電的一篇論文中指出,他們提出了三種新穎的 MLC PCM 技術:1)設備需求平衡,2)基於預測的MSB偏置參考,3)位優先布局,以解決神經網絡應用中的 MLC 設備挑战。使用測量的 MLC 誤碼率,所提出的技術可以將 MLC PCM 保留時間提高105倍,同時將ResNet-20推理精度下降保持在3%以內,並在存在時間阻力漂移的情況下,將CIFAR-100數據集的精度下降減少 91% (10.8X)。如下圖所示。

台積電在PCRAM上的研究(圖源:IEEE)

Ferroelectrics

2011年在摻雜HfO2 ALD多晶薄膜(

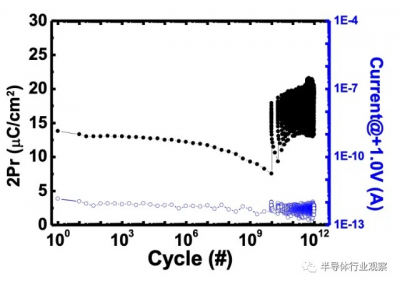

台積電正在探索鐵電薄膜和堆疊及其可控性、狀態保持性、持久性和可擴展性,以實現與先進CMOS技術集成的高密度、高容量數字存儲器。台積電表示,重復循環後殘余極化的退化是可靠性的主要問題,下圖是鐵電 HfZrO 的疲勞表徵及其恢復行爲進行的研究。

鐵電HfZrO的疲勞表徵及其恢復行爲(圖源:IEEE)

選擇器(Selector)

但是要實現高效能和節能的高密度非易失性存儲器,除了上述這幾大新型的存儲材料之外,台積電還在索新的選擇器材料、器件和工藝。

選擇器是一種兩端裝置,它在高於特定電壓時开啓,否則保持關閉狀態。可以通過使用1S1R 結構(1個選擇器+1個存儲器配對)作爲構建塊來實現高密度存儲器架構(例如交叉點陣列)。當這樣的存儲器陣列被適當地偏置以操作選定的存儲器單元時,來自未選定的存儲器單元的潛行電流可以被串聯連接到每個存儲器單元的選擇器消除。爲實現高性能,开發符合特定非易失性存儲器特性的選擇器至關重要。

選擇器的關鍵要求包括通態與斷態電流比(非线性)、高通態電流密度、快速开關速度、高耐力循環、高熱穩定性、易於工藝集成、以及與存儲元件的操作兼容性。

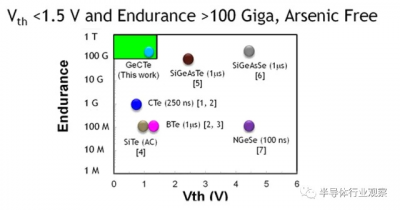

目前業界正在研究四種主要類型的選擇器:Ovonic閾值开關 (OTS)、金屬-離子閾值开關、絕緣體-金屬過渡和隧道勢壘類型。使用OTS選擇器和 PCRAM 的交叉點存儲器陣列作爲存儲級存儲器已經投入生產,但仍有很大的改進空間。高工作電壓是關鍵問題之一。爲了更有效地與邏輯平台一起工作,選擇器和非易失性存儲單元的總工作電壓應與邏輯平台電源電壓兼容(例如,高級節點爲 1.5V)。

低壓選擇器對於高密度非易失性存儲器的低功耗操作至關重要。台積電的一項研究中表明,基於無砷硫族材料的選擇器在閾值電壓~1.3V和泄漏電流~5nA的情況下,具有超過10 11個循環的高壽命。耐久性的提高歸因於適當的摻雜劑抑制相分離,形成更穩定的非晶網絡。

台積電基於無砷硫族化物材料的選擇器

(圖源:IEEE)

寫在最後

就目前新型存儲的商用化進度來看,台積電和英飛凌基於RRAM合作的MCU算是比較快的革新進展,RRAM將有望成爲閃存的替代品。過去幾乎所有的MCU細分市場都使用NOR Flash,但是閃存的微縮化步伐完全趕不上CMOS邏輯的微縮,閃存MCU的量產代際仍停留在40nm節點,而MCU卻已經开始向28nm邁進,而且到了22nm世代以後,CMOS邏輯的晶體管走向FinFET立體化,閃存的MCU研發技術將極其困難。所有的新技術都需要各個產業鏈的通力支持,台積電作爲晶圓代工這一產業鏈上的重要角色,在推動新型存儲發展方面起着很大的作用。

而MRAM則有望成爲SRAM的替代品。台積電作爲先進工藝界的帶頭人,早就感知到了SRAM的微縮進入極限。此前,台積電的一篇論文中表示,SRAM的微縮似乎已經完全崩潰。據WikiChip的報道,在2022年的第68屆年度IEEE國際電子器件會議 (IEDM) 上,台積電談到其新的N3節點中高密度SRAM位單元大小根本沒有縮小,在0.021m處與他們的N5節點的bitcell大小完全相同。然而,在0.0199m,它只有5%的縮放(或0.95倍收縮)。也就是說,台積電的N3B和N3E雖都提供了1.6倍和1.7倍的芯片級晶體管縮放,但SRAM卻只有1倍和1.05倍的縮放。所以對MRAM,台積電進行了多種研究性嘗試。

從台積電的布局中可以看出,台積電採取的是“廣撒網,遍撈魚”的策略,對所有的新型存儲技術都進行探索,因爲每個新型存儲技術都有其獨到的優勢,未來在存儲領域不一定只有一個贏家。

(本文內容編譯自台積電。)

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電正在研究的新型存儲技術

地址:https://www.breakthing.com/post/40037.html