編者按

在AI、5G、大數據中心、汽車等應用快速發展的推動下,電子產品所消耗的電力也在增長。按照nature的統計,預計到2030年,僅ICT所消耗的電力佔比將達到20%以上。因此,芯片設計者或者制造商都爭取在保證芯片性能的情況下,盡可能做到低碳、節能和環保。英諾達本次發布的這款低功耗系列EDA工具,旨在助力IC設計師更好地進行功耗分析!

(2023年4月25日,四川成都)英諾達(成都)電子科技有限公司發布了自主研發的門級功耗分析工具EnFortius凝鋒 Gate-level Power Analyzer(GPA),該軟件是英諾達繼發布低功耗靜態驗證工具LPC之後的第二款低功耗系列EDA工具,可以快速精確地完成門級功耗分析,幫助工程師更好的完成低功耗設計。

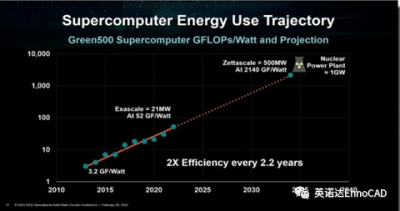

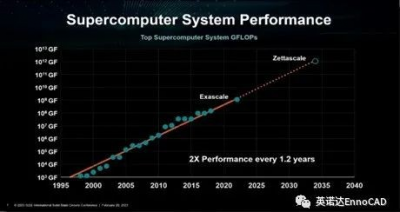

除了性能和面積之外,低功耗長期以來一直是芯片的關鍵設計要求,而功耗面臨的挑战更是與日俱增,甚至成爲制約大算力芯片發展的主要瓶頸。AMD的CEO蘇姿豐日前在ICCSS 2023上表示“現在要讓半導體的算力增加的最大瓶頸,其實不是算力本身而是能耗效率。超級電腦的算力可以每1.2年就翻倍,但是能耗效率的進展卻是每2.2年才能夠翻倍”。

不僅是大算力芯片,低功耗在其他領域也成爲重要的指標。清華大學魏少軍教授在ICCAD 2022會議上提到,中國的IC設計已經到了不能僅靠採取更新的工藝來提升產品競爭力的階段,更多的是需要創新的架構、方法學並配合先進的設計工具來滿足產品競爭力的需求,而低功耗設計就是其中的一條有效途徑。

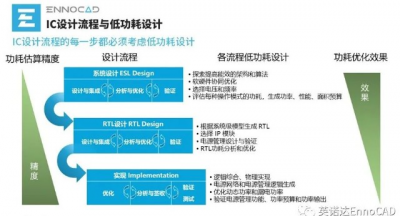

在芯片設計流程中,各個階段都必須考慮低功耗設計,而且每個階段所採取的低功耗策略和使用的工具都略有不同,從整個流程看,越早考慮功耗收益越大,但是估算精度往往不夠精確。到了設計流程後期,特別是物理實現之後,功耗的估算會更精確,但此時可採用的功耗優化方法與優化的程度都比較有限。  IC設計流程與低功耗設計

IC設計流程與低功耗設計

英諾達此次推出的EDA工具GPA是針對門級的功耗分析工具,工具支持工藝庫Liberty標准中的各類功耗模型以及信號活動文件標准SAIF中的各類信號活動信息,比如更精確描述有源器件的SDPD(state-dependent-path-dependent)信號活動信息,同時工具內建算法可以完成信號活動率、信號轉換時間、時鐘信號及特殊常量信號在電路中的傳導計算,准確快速地完成網表級的功耗分析。配合工具提供的各類報告、電路搜索及查詢功能,可以幫助工程師快速有效地定位電路中可能的功耗熱點及分析原因,爲後續的功耗優化提供數據及解決辦法。

英諾達創始人、CEO王琦博士表示:“功耗是IC設計流程中非常重要的一個考慮指標,針對邏輯綜合及物理實現後的網表,英諾達的GPA功耗分析軟件可以快速完成電路的靜態功耗分析,並針對電路中已有的功耗優化方案做評估,爲工程師做進一步功耗優化提供基礎。英諾達未來將在該領域持續發力,立足客戶需求,提供更多更卓越的低功耗設計相關的EDA工具和解決方案。”

關於英諾達

英諾達(成都)電子科技有限公司是一家由行業頂尖資深人士創立的本土EDA企業,公司堅持以客戶需求爲導向,幫助客戶實現價值最大化,爲中國半導體產業提供卓越的EDA解決方案。其自主研發的EnFortius系列低功耗EDA工具,可有效幫助IC設計工程師定位並分析低功耗設計相關問題。此外,英諾達可提供完整、可定制的前/後端設計服務,其一站式驗證解決方案可爲廠商提高芯片設計效率。公司的長期目標是通過EDA工具的研發和上雲實踐,參與國產EDA完整工具鏈布局並探索適合中國國情的工業軟件上雲的路徑與模式,賦能半導體產業高質量發展。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

今天是《半導體行業觀察》爲您分享的第3382期內容,歡迎關注。

推薦閱讀

L4緩存,有望走向主流?

中國SiC,“挖坑”了嗎?

蘋果,終於在芯片上認命

半導體行業觀察

『半導體第一垂直媒體』

實時 專業 原創 深度

識別二維碼,回復下方關鍵詞,閱讀更多

晶圓|集成電路|設備|汽車芯片|存儲|台積電|AI|封裝

回復 投稿,看《如何成爲“半導體行業觀察”的一員 》

回復 搜索,還能輕松找到其他你感興趣的文章!

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:英諾達再發低功耗EDA工具,將持續在該領域發力

地址:https://www.breakthing.com/post/54602.html