來源:內容由半導體行業觀察編譯自anandtech,謝謝。

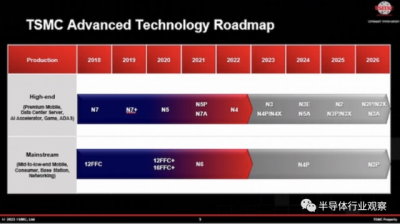

在今天舉行的 2023 年北美技術研討會上,台積電披露了有關其即將在 2025 年至 2026 年及以後推出的 N2 2nm 級生產節點計劃的更多詳細信息。台積電的 N2 制造技術系列將隨着更多變化而擴展,包括具有背面供電的 N2P 和用於高性能計算的 N2X。在這些即將到來的 N2 代工藝節點之間,台積電正在制定路线圖,以繼續其提高晶體管性能效率、優化功耗和提高晶體管密度的不懈步伐。

N2 密度更高

台積電去年推出的初始N2 制造工藝將成爲代工廠龍頭第一個使用環柵 (GAAFET) 晶體管的節點,台積電將其稱爲 Nanosheet 晶體管。GAAFET 相對於當前 FinFET 晶體管的優勢包括更低的漏電流(因爲柵極存在於溝道的所有四個側面),以及調整溝道寬度以實現更高性能或更低功耗的能力。

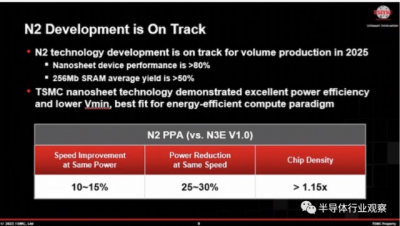

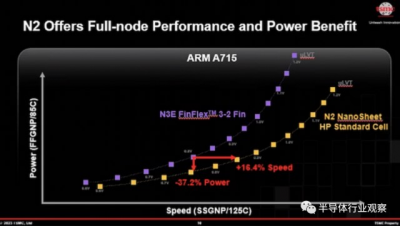

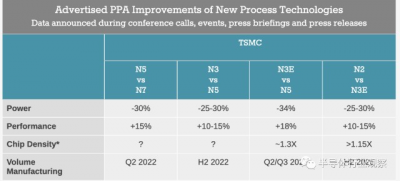

台積電在去年推出這項技術時表示,在相同的功率和復雜度下,可以將晶體管性能提升 10% 到 15%,或者在相同的時鐘和晶體管數量下,將功耗降低 25% 到 30%。該公司還表示,N2 將提供比N3E高 15% 以上的“混合”芯片密度,這比去年宣布的 10% 密度增加有所增加。

今天,該公司表示 N2 技術开發步入正軌,該節點將在 2025 年(可能是 2025 年很晚)進入大批量生產。該公司還表示,在進入 HVM 前兩年,其 Nanosheet GAA 晶體管性能已達到其目標規格的 80% 以上,並且 256Mb SRAM 測試 IC 的平均良率超過 50%。

“台積電納米片技術展示了出色的電源效率和更低的 Vmin,最適合節能計算範式,”台積電的一份聲明中寫道。

N2P在2026年獲得背面供電

台積電的 N2 系列將在 2026 年的某個時候發展,屆時該公司計劃推出其 N2P 制造技術。N2P 將爲 N2 的 Nanosheet GAA 晶體管添加背面電源軌。

背面供電旨在通過將電源軌移至背面來解耦 I/O 和電源布线,從而解決後端线路 (BEOL) 中過孔電阻升高等挑战。反過來,這將提高晶體管性能並降低其功耗。此外,背面供電消除了數據和電源連接之間的一些潛在幹擾。

背面供電是一項創新,其重要性怎么強調都不爲過。多年來,芯片制造商一直在與芯片供電電路中的阻力作鬥爭,而背面供電網絡 (PDN) 是解決這些問題的另一種方法。此外,去耦 PDN 和數據連接也有助於減少面積,因此與 N2 相比,N2P 有望進一步提高晶體管密度。

目前,台積電並未透露任何有關 N2P 相對於 N2 的性能、功耗和面積 (PPA) 優勢的具體數字。但根據我們從業內人士那裏聽到的消息,單是背面電源軌就可以帶來個位數的功率改進和兩位數的晶體管密度改進。

台積電表示,N2P 有望在 2026 年投產,因此我們可以推測,首款基於 N2P 的芯片將於 2027 年上市。這個時間表將使台積電在背面功率方面落後競爭對手英特爾大約兩年,假設他們能夠在 2024 年按時交付自己的 20A 工藝。

N2X:更高的性能

除了可能成爲台積電 2nm 代工藝的主力軍的 N2P 之外,台積電還在准備 N2X。這將是一種爲高性能計算 (HPC) 應用量身定制的制造工藝,例如需要更高電壓和時鐘的高端 CPU。代工廠並未概述該節點與 N2、N2P 和 N3X 相比的具體優勢,但與所有性能增強節點一樣,實際優勢預計將在很大程度上取決於實施了多少設計技術協同優化 (DTCO) .

在介紹2nm的同時,台積電在技術研討會上海深入介紹了公司3nm的演進路线。

詳細介紹3nm的演進

3nm是台積電最後一代基於 FinFET 的工藝節點,N3 系列預計將在未來許多年內以某種形狀或形式存在,作爲不需要更先進的基於 GAAFET 工藝的客戶可用的最密集節點。

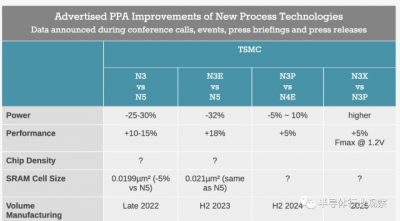

台積電在 N3 前端的重大路线圖更新是 N3P 及其高性能變體 N3X。正如台積電今天透露的那樣,N3P 將是 N3E 的光學縮小版,與 N3E 相比,提供增強的性能、更低的功耗和更高的晶體管密度,同時保持與 N3E 設計規則的兼容性。同時,N3X 將極致性能與 3 納米級密度相結合,爲高性能 CPU 和其他處理器提供更高的時鐘速度。

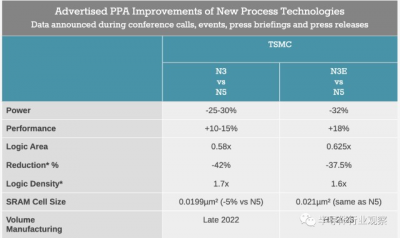

作爲快速復習,台積電的 N3(3 納米級)工藝技術系列由多種變體組成,包括基准 N3(又名 N3B)、降低成本的寬松 N3E、具有增強性能和芯片密度的 N3P 以及具有更高電壓容限的 N3X . 去年該公司還談到了具有最大化晶體管密度的 N3S,但今年該公司對這個節點守口如瓶,幻燈片中的任何地方都沒有提到它。

台積電的普通 N3 節點具有多達 25 個 EUV 層,台積電在其中一些層上使用 EUV 雙圖案,以實現比 N5 更高的邏輯和 SRAM 晶體管密度。EUV 步驟通常很昂貴,而 EUV 雙圖案化進一步推高了這些成本,這就是爲什么這種制造工藝預計只會被少數不關心所需高額支出的客戶使用。

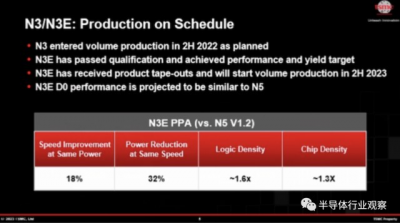

大多數對 3nm 級工藝感興趣的台積電客戶預計將使用寬松的 N3E 節點,根據台積電的說法,該節點正在按計劃實現其性能目標。N3E 使用多達 19 個 EUV 層,完全不依賴 EUV 雙圖案化,降低了其復雜性和成本。權衡是 N3E 提供比 N3 更低的邏輯密度,並且它具有與 TSMC 的 N5 節點相同的 SRAM 單元尺寸,這使得它對那些追求密度/面積增益的客戶的吸引力有所降低。總體而言,N3E 有望提供更寬的工藝窗口和更高的良率,這是芯片制造中的兩個關鍵指標。

台積電業務發展副總裁 Kevin Zhang 表示:“N3E 在良率、工藝復雜性方面將優於 N3,這直接轉化爲 [更寬的] 工藝窗口。”

在 N3E 之後,台積電將繼續使用 N3P 優化 N3 系列的晶體管密度,N3P 將通過提供改進的晶體管特性建立在 N3E 的基礎上。改進的工藝節點將使芯片設計人員能夠在相同的泄漏下將性能提高 5%,或者在相同的時鐘下將功耗降低 5% ~ 10%。新節點還將爲“混合”芯片設計增加 4% 的晶體管密度,台積電將其定義爲由 50% 邏輯、30% SRAM 和 20% 模擬電路組成的芯片。

作爲他們對 N3P 討論的一部分,台積電強調密度的提高是通過調整其掃描儀的光學性能來實現的。因此,台積電很可能會在這裏縮小所有類型的芯片結構,這將使 N3P 成爲 SRAM 密集型設計的一個有吸引力的節點。

“N3P 是一種性能提升,它的性能提高了 5%,至少比 N3E 高出 5%,”張解釋說。它還具有 2% 的光學收縮,使晶體管密度達到 1.04 倍。”

由於N3P是N3E的光縮,它會保留N3E的設計規則,使芯片設計者能夠在新節點上快速復用N3E IP。因此,N3P 預計也將成爲 TSMC 最受歡迎的 N3 節點之一,因此預計 Cadence 和 Synopsys 等 IP 設計公司將爲該工藝技術提供各種 IP,從而在工藝中獲得與現有 N3E 的前向兼容性優勢。台積電表示,N3P 將於 2024 年下半年量產。

最後,對於 CPU 和 GPU 等高性能計算應用程序的开發人員,台積電在過去幾代中一直提供其 X 系列高壓、以性能爲中心的節點。正如在去年的活動中所披露的那樣,N3 系列將擁有自己的 X 變體,並帶有恰當命名的 N3X 節點。

與 N3E 相比,N3X 預計提供至少比 N3P 高 5% 的時鐘速度。這是通過使節點更能承受更高電壓來實現的,允許芯片設計人員提高時鐘速度以換取更高的整體泄漏。

台積電聲稱 N3X 將支持(至少)1.2v 的電壓,這對於 3nm 級制造工藝來說是一個相當極端的電壓。反過來,泄漏成本也很高,台積電預計在更平衡的 N3P 節點上功率泄漏將增加 250%。這強調了爲什么 N3X 實際上只適用於 HPC 級處理器,並且芯片設計人員需要格外小心,以控制他們最強大(和耗電)的芯片。

至於晶體管密度,N3X 將提供與 N3P 相同的密度。台積電還沒有評論它是否也會保持與 N3P 和 N3E 的設計規則兼容,所以看看最終會發生什么將會很有趣。

台積電當前路线圖中的最後一個 N3 系列節點,該公司表示 N3X 將於 2025 年投入生產。

更多技術發布

在會上,台積電還披露了TSMC 3DFabric先進封裝和硅堆疊——TSMC 3DFabric 系統集成技術的主要新發展,當中包括:

先進封裝——爲了支持 HPC 應用在單個封裝中容納更多處理器和內存的需求,台積電正在开發基板上晶圓上芯片 (CoWoS) 解決方案,該解決方案具有高達 6 倍光罩尺寸(~5,000mm2)的 RDL 中介層,能夠可容納 12 個 HBM 內存堆棧。

3D 芯片堆疊——台積電宣布推出 SoIC-P,這是其集成芯片系統 (SoIC) 解決方案的微凸塊版本,爲 3D 芯片堆疊提供了一種經濟高效的方式。SoIC-P 補充了 TSMC 現有的用於高性能計算 (HPC) 應用的無擾動解決方案,這些解決方案現在稱爲 SoIC-X。

設計支持——台積電推出了 3Dblox 1.5,這是其开放標准設計語言的最新版本,旨在降低 3D IC 設計的門檻。3Dblox 1.5 添加了自動凸點合成,幫助設計人員處理具有數千個凸點的大型芯片的復雜性,並有可能將設計時間縮短數月。

台積電還表示,今年將發布新軟件,以幫助开發先進汽車計算機芯片的客戶更快地利用其最新技術。

台積電是全球最大的半導體合約制造商。恩智浦半導體和意法半導體等許多汽車行業最大的芯片供應商都選擇台積電制造芯片。但與消費電子產品中的芯片相比,汽車芯片必須滿足更高的堅固性和壽命標准。台積電擁有用於汽車行業的特殊制造工藝,通常比消費類芯片的類似工藝晚幾年。

過去,汽車芯片公司需要額外的時間來爲那些專門的生產线創建芯片設計。結果是汽車芯片可能比最新智能手機中的芯片落後數年。在技術大會上,台積電推出了新軟件,使汽車芯片設計人員能夠提前兩年左右开始設計工作。這將使這些公司能夠使用台積電 N3 芯片制造技術的汽車版本——這是消費設備的當前技術水平——一旦台積電在 2025 年推出汽車級版本。

“從歷史上看,汽車一直遠遠落後於消費者,”台積電業務發展副總裁 Kevin Zhang 在新聞發布會上表示。“那是過去。這使我們的汽車客戶能夠更早地开始他們的設計——事實上,比之前早了兩年。”

張說,在大流行和隨之而來的汽車半導體短缺之前,汽車制造商通常將重要的芯片技術決策留給供應商。但現在,這些供應商和汽車制造商經常與台積電直接討論。“他們充分意識到他們需要直接接觸硅技術選擇,”張說。“在過去的幾年裏,我親自會見了許多主要的汽車業首席執行官。...我們在前期與他們密切合作。”

參考文獻

https://www.anandtech.com/show/18832/tsmc-outlines-2nm-plans-n2p-brings-backside-power-delivery-in-2026-n2x-added-to-roadmap

https://www.anandtech.com/show/18833/tsmc-details-3nm-evolution-n3e-on-schedule-n3p-n3x-deliver-five-percent-gains

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電深度披露2nm,,介紹3nm的演進

地址:https://www.breakthing.com/post/55135.html