來源:內容由半導體行業觀察綜合自工商時報,謝謝。

晶圓代工龍頭台積電日前召开法人說明會,重申基於支援客戶中長期結構性需求,今年320億至360億美元資本支出計劃不變。設備業者分析,台積電資本支出7成用於先進制程,雖然市況低迷但仍維持投資金額不變,主要是策略上集中資源加快興建2納米晶圓廠,拉开與競爭同業技術及產能差距。

台積電已經啓動2納米技術研發並开始新晶圓廠興建計畫,2納米晶圓廠預計會落腳在新竹與台中科學園區,共計有六期工程。根據台積電公布資料,台積電在竹科寶山二期興建的2納米超大型晶圓廠Fab 20,將會興建第一期到第四期共四座晶圓廠,台積電正在爭取中科台中園區擴建二期开發計劃建廠用地,會再興建二座2納米晶圓廠。

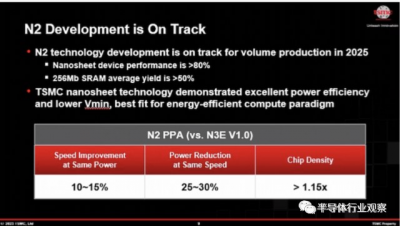

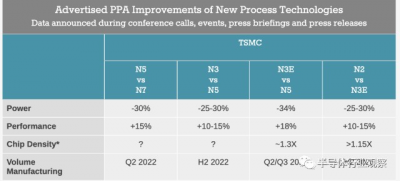

設備業者推估,台積電2納米共六座晶圓廠的投資總金額將超過1,200億美元,約折合新台幣3.6兆元,會是台灣科技業有史以來規模最大的投資案,這也是台積電沒有調降今年資本支出的關鍵原因之一。台積電雖然面對地緣政治風險,已在中國、美國、及日本設廠,也計劃在歐洲投資,但台灣仍會是最先進制程的最優先選擇。至於2納米進度部份,台積電在日前召开的2023年北美技術論壇中,宣布2納米技術开發進展良好,在良率與元件效能上皆展現良好的進展,將如期於2025年量產。相較3納米加強版N3E制程,2納米在相同功耗下速度最快將可增加至15%,在相同速度下功耗最多可降低30%,同時芯片密度增加大於15%。

台積電深度披露2nm

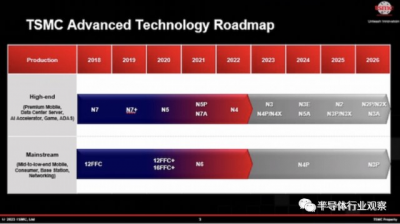

在之前舉行的 2023 年北美技術研討會上,台積電披露了有關其即將在 2025 年至 2026 年及以後推出的 N2 2nm 級生產節點計劃的更多詳細信息。台積電的 N2 制造技術系列將隨着更多變化而擴展,包括具有背面供電的 N2P 和用於高性能計算的 N2X。在這些即將到來的 N2 代工藝節點之間,台積電正在制定路线圖,以繼續其提高晶體管性能效率、優化功耗和提高晶體管密度的不懈步伐。

N2 密度更高

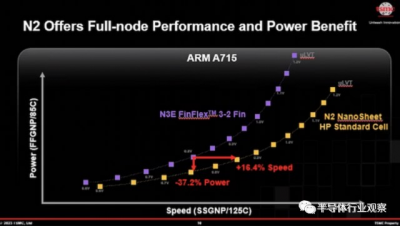

台積電去年推出的初始N2 制造工藝將成爲代工廠龍頭第一個使用環柵 (GAAFET) 晶體管的節點,台積電將其稱爲 Nanosheet 晶體管。GAAFET 相對於當前 FinFET 晶體管的優勢包括更低的漏電流(因爲柵極存在於溝道的所有四個側面),以及調整溝道寬度以實現更高性能或更低功耗的能力。

台積電在去年推出這項技術時表示,在相同的功率和復雜度下,可以將晶體管性能提升 10% 到 15%,或者在相同的時鐘和晶體管數量下,將功耗降低 25% 到 30%。該公司還表示,N2 將提供比N3E高 15% 以上的“混合”芯片密度,這比去年宣布的 10% 密度增加有所增加。

今天,該公司表示 N2 技術开發步入正軌,該節點將在 2025 年(可能是 2025 年很晚)進入大批量生產。該公司還表示,在進入 HVM 前兩年,其 Nanosheet GAA 晶體管性能已達到其目標規格的 80% 以上,並且 256Mb SRAM 測試 IC 的平均良率超過 50%。

“台積電納米片技術展示了出色的電源效率和更低的 Vmin,最適合節能計算範式,”台積電的一份聲明中寫道。

N2P在2026年獲得背面供電

台積電的 N2 系列將在 2026 年的某個時候發展,屆時該公司計劃推出其 N2P 制造技術。N2P 將爲 N2 的 Nanosheet GAA 晶體管添加背面電源軌。

背面供電旨在通過將電源軌移至背面來解耦 I/O 和電源布线,從而解決後端线路 (BEOL) 中過孔電阻升高等挑战。反過來,這將提高晶體管性能並降低其功耗。此外,背面供電消除了數據和電源連接之間的一些潛在幹擾。

背面供電是一項創新,其重要性怎么強調都不爲過。多年來,芯片制造商一直在與芯片供電電路中的阻力作鬥爭,而背面供電網絡 (PDN) 是解決這些問題的另一種方法。此外,去耦 PDN 和數據連接也有助於減少面積,因此與 N2 相比,N2P 有望進一步提高晶體管密度。

目前,台積電並未透露任何有關 N2P 相對於 N2 的性能、功耗和面積 (PPA) 優勢的具體數字。但根據我們從業內人士那裏聽到的消息,單是背面電源軌就可以帶來個位數的功率改進和兩位數的晶體管密度改進。

台積電表示,N2P 有望在 2026 年投產,因此我們可以推測,首款基於 N2P 的芯片將於 2027 年上市。這個時間表將使台積電在背面功率方面落後競爭對手英特爾大約兩年,假設他們能夠在 2024 年按時交付自己的 20A 工藝。

N2X:更高的性能

除了可能成爲台積電 2nm 代工藝的主力軍的 N2P 之外,台積電還在准備 N2X。這將是一種爲高性能計算 (HPC) 應用量身定制的制造工藝,例如需要更高電壓和時鐘的高端 CPU。代工廠並未概述該節點與 N2、N2P 和 N3X 相比的具體優勢,但與所有性能增強節點一樣,實際優勢預計將在很大程度上取決於實施了多少設計技術協同優化 (DTCO) 。

在介紹2nm的同時,台積電在技術研討會上海深入介紹了公司3nm的演進路线。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電:2nm建加速

地址:https://www.breakthing.com/post/55604.html