來源:內容來自半導體行業觀察綜合,謝謝。

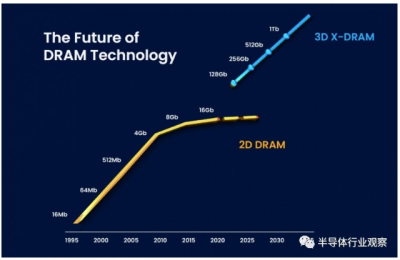

初創公司 NEO Semiconductor 表示,其 3D X-DRAM 技術可以生產 230 層的 128Gbit DRAM 芯片——是當前 DRAM 密度的八倍。

NEO 專注於半導體存儲器並开發了X-NAND技術,NAND 芯片具有多個平行平面以加速數據訪問——第一代順序寫入帶寬爲 1,600MBps,第二代爲 3,200MBps。它表示全行業都在努力將 3D 單元帶入 DRAM 的方法,NEO 現在擁有 3D DRAM 技術。與 3D NAND 一樣,它可以顯着提高 DRAM 密度。

該公司聯合創始人兼首席執行官 Andy Hsu 樂觀地表示:“3D X-DRAM 將是半導體行業未來絕對的增長動力。” Hsu 於 1995 年從倫斯勒理工學院獲得碩士學位後,在一家未命名的半導體初創公司工作了 16 年。他於 2012 年 8 月創立了 NEO Semiconductor,並擁有 12 項專利。NEO本身擁有23項專利。

他補充說:“今天我可以自信地說,NEO 正在成爲 3D DRAM 市場的明顯領導者。與當今市場上的其他解決方案相比,我們的發明非常簡單,制造和規模化成本更低。通過我們的 3D X-DRAM,業界有望每十年實現 8 倍的密度和容量提升。”

NEO 表示,3D X-DRAM 是解決由下一波 AI 應用(例如 ChatGPT)驅動的對高性能和大容量存儲器半導體的需求增長所必需的。

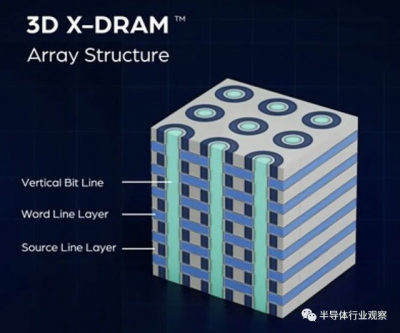

一張圖展示了 3D X-DRAM 的概念:

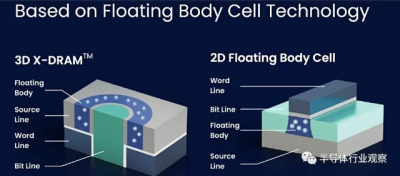

該概念具有基於無電容器浮體單元 (FBC) 技術的類 3D NAND DRAM 單元陣列結構。這種 FBC 技術使用一個晶體管和零個電容器將數據存儲爲電荷。NEO 表示它可以使用當前的 3D NAND 類工藝制造,並且只需要一個掩模來定義位线孔並在孔內形成單元結構。這提供了一種高速、高密度、低成本和高產量的制造解決方案,這是一個重要的主張。

全行業正在努力將 3D 引入 DRAM。採用 3D X-DRAM™ 僅涉及利用當前成熟的 3D NAND 工藝,這與學術論文提出和內存行業研究的許多將 DRAM 遷移到 3D 的替代方案不同。如果沒有 3D X-DRAM™,該行業將面臨潛在的等待數十年,應對不可避免的制造中斷,並減輕不可接受的產量和成本挑战。3D X-DRAM™ 是滿足由 ChatGPT 等下一波人工智能 (AI) 應用推動的對高性能和大容量存儲器半導體需求增長的必要解決方案。

Network Storage Advisors 總裁Jay Kramer表示:“從 2D 到 3D 架構的發展爲 NAND 閃存帶來了引人注目且極具價值的優勢,因此在整個行業範圍內實現 DRAM 的類似發展是非常可取的。” “NEO Semiconductor 的創新 3D X-DRAM™ 允許內存行業利用當前的技術、節點和工藝來增強具有 NAND 類 3D 架構的 DRAM 產品。”

據了解,NEO 將尋求將其技術授權給 DRAM 制造公司,例如美光、三星和 SK 海力士。Kioxia 和 Western Digital 等 NAND 制造商也可能獲得許可。

3D-NAND 閃存,探索超過 300 層

在即將舉行的 2023 年 VLSI 技術和電路研討會上,多篇論文涵蓋了 3D-NAND 閃存非易失性存儲器。會議定於 6 月 11 日至 16 日在日本京都舉行。

來自 Kioxia Corp. 的論文 C2-1,“A 1Tb 3b/Cell 3D-Flash Memory of more than 17Gb/mm2 bit Density with 3.2Gbps Interface and 205MB/s Program Throughput”提供了使用 210 個字线層的單片 1Tbit 存儲器. 這代表了使用 3.2Gbps 讀取接口和每秒 205MB 編程量進行優化的練習。該組件每個存儲單元存儲三位,並實現每平方毫米 17Gbits 的密度。

物理 8 平面架構實現了 40 微秒的讀取延遲和每秒 205 字節的高程序量。單脈衝雙頻閃技術將感測時間減少了 18%,並有助於實現 205MB/s 的程序量。

Kioxia 和長期合作夥伴 Western Digital 的研究人員將提交論文 T7-1 “Highly Scalable Metal Induced Lateral Crystallization (MILC) Techniques for Vertical silicon Channel in Ultra-High (> 300 Layers) 3D Flash Memory”

金屬誘導的橫向結晶允許在超過 300 層的垂直存儲孔中形成 14 微米長的“通心粉”格式通道。作者描述了最近开發的鎳吸雜技術。112 字线分層 3D NAND 閃存在不降低存儲單元可靠性的情況下,讀取噪聲降低了 40% 以上,通道傳導性能提高了 10 倍。

半導體制造設備供應商 Tokyo Electron Ltd. 的一篇論文幫助繪制了一種 400 多層 3D-NAND 閃存的方法,使當今的商業技術水平翻了一番。

論文 T3-2 是“Beyond 10 micron Depth Ultra-High Speed Etch Process with 84% Lower Carbon Footprint for Memory Channel Hole of 3D NAND Flash over 400 Layers.” Tokyo Electron Miyagi 的作者在本文中討論了一種使用低溫和無碳化學進行高縱橫比孔圖案化的新型蝕刻工藝。作者發現,可以在大約 33 分鐘的時間內將孔蝕刻到晶圓上 10 微米深。據說蝕刻剖面非常好。與其他蝕刻工藝相比,溫室氣體排放量減少了 84%。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:全球首款3DDRAM,NANDFlash奔向300層

地址:https://www.breakthing.com/post/56119.html