來源:內容由半導體行業觀察編譯自anandtech,謝謝。

三星晶圓廠將在即將於日本京都舉行的2023 年超大規模集成電路技術和電路研討會上詳細介紹其第二代 3 納米級制造技術以及性能增強的 4 納米級制造工藝。這兩種技術對於芯片合同制造商都很重要,因爲 SF3 (3GAP) 承諾爲移動和 SoC 提供切實的改進,而 SF4X (N4HPC) 專爲要求最苛刻的高性能計算 (HPC) 應用而設計。

具有 GAA 晶體管的第二代 3 納米節點

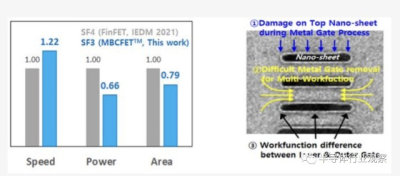

三星即將推出的 SF3 (3GAP) 工藝技術是該公司 SF3E (3GAE) 制造工藝的增強版,並依賴於其第二代環柵晶體管——該公司稱之爲多橋通道場效應晶體管 ( MBCFET)。該節點承諾進行額外的工藝優化,盡管晶圓廠不希望將 SF3 與 SF3E 進行比較。與其直接前身 SF4(4LPP,4nm 級,超低功耗)相比,SF3 聲稱在相同的功率和復雜性下性能提升 22%,或在相同的時鐘和晶體管數量下功率降低 34%,以及邏輯面積減少 21%。盡管尚不清楚該公司是否已實現 SRAM 和模擬電路的任何擴展。

此外,三星聲稱 SF3 將提供額外的設計靈活性,通過在同一單元類型中改變 MBCFET 器件的納米片 (NS) 溝道寬度來促進。奇怪的是,可變溝道寬度是 GAA 晶體管的一個特性,已經討論了多年,因此三星在 SF3 上下文中的措辭方式可能意味着 SF3E 不支持它。

迄今爲止,該集團的芯片开發部門三星 LSI 和三星代工廠的其他客戶都沒有正式推出採用 SF3E/3GAE 工藝技術量產的單一高度復雜處理器。事實上,據TrendForce稱,使用業界首個 3 納米級制造工藝的唯一公开認可的應用似乎是加密貨幣挖礦芯片 。這並不奇怪,因爲三星“早期”節點的使用通常非常有限。

相比之下,三星的“plus”技術通常被廣泛的客戶使用,因此該公司的 SF3 (3GAP) 工藝在 2024 年某個時候可用時可能會看到更高的產量。

用於超高性能應用的 SF4X

除了專爲各種可能的用例而設計的 SF3 之外,三星代工廠正在准備其 SF4X(4HPC,4 納米級高性能計算),專爲面向數據中心的 CPU 和 GPU 等性能要求苛刻的應用而設計。

爲解決此類芯片問題,三星的 SF4X 提供了 10% 的性能提升和 23% 的功耗降低。三星沒有明確說明比較的工藝節點是什么,但據推測,這是針對他們默認的 SF4 (4LPP) 制造技術。爲實現這一目標,三星在重新評估晶體管的應力(大概在高負載下)後重新設計了晶體管的源極和漏極,進一步進行了晶體管級設計技術協同優化 (T-DTCO),並引入了新的中間线 (MOL) ) 方案。

新的 MOL 使 SF4X 能夠提供 60mV 的經過硅驗證的 CPU 最小電壓 (Vmin),斷態電流 (IDDQ) 的變化減少 10%,保證在 1V 以上的高壓 (Vdd) 運行而不會降低性能,以及改進的 SRAM 工藝余量。

三星的 SF4X 將成爲台積電 N4P 和 N4X 節點的競爭對手,它們分別將於 2024 年和 2025 年到期。僅根據聲明的規格,很難判斷哪種技術將提供性能、功率、晶體管密度、效率和成本的最佳組合。也就是說,SF4X 將是三星近年來第一個專門爲 HPC 設計的節點,這意味着三星有(或正在期待)足夠的客戶需求,值得他們花時間。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:三星第二代3nm,更多細節曝光!

地址:https://www.breakthing.com/post/57533.html