來源:內容來自三星,謝謝。

先進半導體技術的全球領導者三星電子今天宣布,开發出業界首款支持 Compute Express Link (CXL) 2.0 的 128 GB DRAM。三星與英特爾密切合作,在英特爾至強平台上實現這一具有裏程碑意義的進步。

在 2022 年 5 月开發出業界首款基於 CXL 1.1 的 CXL DRAM 的基礎上,三星推出基於 CXL 2.0 的 128GB CXL DRAM 有望加速下一代內存解決方案的商業化。新的 CXL DRAM 支持 PCle 5.0 接口(x8 通道)並提供高達每秒 35GB 的帶寬。

“作爲 CXL 聯盟董事會成員,三星電子始終處於 CXL 技術的前沿,”三星電子新業務規劃團隊副總裁 Jangseok Choi 表示。“這一突破性的發展突顯了我們通過與整個行業的數據中心、服務器和芯片組公司合作進一步擴展 CXL 生態系統的承諾。”

英特爾公司技術計劃總監 Jim Pappas 表示:“英特爾很高興與三星合作,投資於充滿活力的 CXL 生態系統。英特爾將繼續與三星合作,促進創新 CXL 產品在整個行業的發展和採用。”

“瀾起科技很高興能夠量產第一款支持 CXL 2.0 的控制器,”瀾起科技總裁 Stephen Tai 表示。“我們期待繼續與三星合作,以推進 CXL 技術並擴展其生態系統。”

CXL 2.0 有史以來第一次支持內存池——一種內存管理技術,可將服務器平台上的多個 CXL 內存塊綁定在一起形成池,並使主機能夠根據需要從池中動態分配內存。新技術使客戶能夠在降低運營成本的同時最大限度地提高效率,這反過來又將幫助客戶將資源重新投入到增強服務器內存中。

三星計劃在今年晚些時候开始量產 CXL 2.0 DRAM,並准備提供各種容量的額外產品以滿足未來計算應用的需求。

CXL 是下一代接口,可提高高性能服務器系統中與 CPU 一起使用的加速器、DRAM 和存儲設備的效率。鑑於其帶寬和容量在與主 DRAM 一起使用時可以擴展,該技術的進步有望在人工智能 (AI) 和機器學習 (ML) 等關鍵技術引領的下一代計算市場掀起波瀾。對高速數據處理的需求迅速上升。

關於CXL,你想知道的都在這裏

指數級的數據增長促使計算行業开始進行突破性的架構轉變,以從根本上改變數據中心的性能、效率和成本。

爲了繼續提高性能,服務器正越來越多地轉向異構計算架構,使用專門構建的加速器從 CPU 卸載專門的工作負載。CXL 的內存緩存一致性允許在 CPU 和加速器之間共享內存資源。

此外,CXL 支持部署新的內存層,可以彌合主內存和 SSD 存儲之間的延遲差距。這些新的內存層將增加帶寬、容量、提高效率並降低總體擁有成本 (TCO)。憑借這些諸多優勢,業界果斷地將 CXL 融合爲處理器、內存和加速器的高速緩存一致性互連。

CXL通過一個叫做CXL 聯盟的开放行業標准組織开發技術規範,促進新興使用模型的性能突破,同時支持數據中心加速器和其他高速增強功能的开放生態系統。

CXL簡介:什么是 Compute Express Link?

CXL是一個开放標准的行業支持的緩存一致性互連,用於處理器、內存擴展和加速器。從本質上講,CXL 技術在 CPU 內存空間和連接設備上的內存之間保持內存一致性。這支持資源共享(或池化)以獲得更高的性能,降低軟件堆棧的復雜性,並降低整體系統成本。CXL 聯盟已經確定了將採用新互連的三類主要設備:

類型1設備:智能 NIC 等加速器通常缺少本地內存。通過 CXL,這些設備可以與主機處理器的 DDR 內存進行通信。

類型2設備:GPU、ASIC 和 FPGA 都配備了 DDR 或 HBM 內存,並且可以使用 CXL 使主機處理器的內存在本地可供加速器使用,並使加速器的內存在本地可供 CPU 使用。它們還共同位於同一個緩存一致域中,有助於提升異構工作負載。

類型 3 設備:內存設備可以通過 CXL 連接,爲主機處理器提供額外的帶寬和容量。內存的類型獨立於主機的主內存。

CXL 協議和標准

CXL 標准通過三種協議支持各種用例:CXL.io、CXL.cache 和 CXL.memory。

CXL.io:該協議在功能上等同於 PCIe 協議,並利用了 PCIe 的廣泛行業採用和熟悉度。作爲基礎通信協議,CXL.io 用途廣泛,適用於廣泛的用例。

CXL.cache:該協議專爲更具體的應用程序而設計,使加速器能夠有效地訪問和緩存主機內存以優化性能。

CXL.memory:該協議使主機(例如處理器)能夠使用加載/存儲命令訪問設備連接的內存。

這三個協議共同促進了計算設備(例如 CPU 主機和 AI 加速器)之間內存資源的一致共享。從本質上講,這通過共享內存實現通信簡化了編程。用於設備和主機互連的協議如下:

類型 1 設備:CXL.io + CXL.cache

類型2設備:CXL.io + CXL.cache + CXL.memory

類型 3 設備:CXL.io + CXL.memory

Compute Express Link 與 PCIe:這兩者有什么關系?

CXL 建立在PCIe的物理和電氣接口之上,其協議建立了一致性、簡化了軟件堆棧並保持與現有標准的兼容性。具體來說,CXL 利用 PCIe 5 功能,允許備用協議使用物理 PCIe 層。當支持 CXL 的加速器插入 x16 插槽時,設備會以每秒 2.5 千兆傳輸 (GT/s) 的默認 PCI Express 1.0 傳輸速率與主機處理器的端口進行協商。只有雙方都支持 CXL,CXL 交易協議才會被激活。否則,它們作爲 PCIe 設備運行。

CXL 1.1 和 2.0 使用 PCIe 5.0 物理層,允許通過 16 通道鏈路在每個方向上以 32 GT/s 或高達 64 GB/s 的速度傳輸數據。

CXL 3.0 使用 PCIe 6.0 物理層將數據傳輸擴展到 64 GT/s,支持通過 x16 鏈路進行高達 128 GB/s 的雙向通信。

CXL 2.0 和 3.0 有什么新功能?

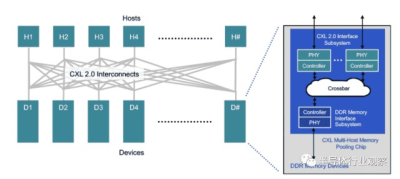

首先在內存池方面,CXL 2.0 支持切換以啓用內存池。使用 CXL 2.0 交換機,主機可以訪問池中的一個或多個設備。盡管主機必須支持 CXL 2.0 才能利用此功能,但內存設備可以是支持 CXL 1.0、1.1 和 2.0 的硬件的組合。在 1.0/1.1 中,設備被限制爲一次只能由一台主機訪問的單個邏輯設備。然而,一個 2.0 級別的設備可以被劃分爲多個邏輯設備,允許多達 16 台主機同時訪問內存的不同部分。

例如,主機 1 (H1) 可以使用設備 1 (D1) 中一半的內存和設備 2 (D2) 中四分之一的內存,以將其工作負載的內存需求與內存池中的可用容量完美匹配. 設備 D1 和 D2 中的剩余容量可由一台或多台其他主機使用,最多可達 16 台。設備 D3 和 D4 分別啓用了 CXL 1.0 和 1.1,一次只能由一台主機使用。

CXL 3.0 引入了對等直接內存訪問和對內存池的增強,其中多個主機可以一致地共享 CXL 3.0 設備上的內存空間。這些功能支持新的使用模型並提高數據中心架構的靈活性。

其次來到交換方面;

通過轉向 CXL 2.0 直連架構,數據中心可以獲得主內存擴展的性能優勢,以及池內存的效率和總體擁有成本 (TCO) 優勢。假設所有主機和設備都支持 CXL 2.0,則“切換”通過 CXL 內存池芯片中的交叉开關集成到內存設備中。這可以保持較低的延遲,但需要更強大的芯片,因爲它現在負責交換機執行的控制平面功能。通過低延遲直接連接,連接的內存設備可以使用 DDR DRAM 來擴展主機主內存。這可以在非常靈活的基礎上完成,因爲主機能夠訪問處理特定工作負載所需的盡可能多的設備的全部或部分容量。

CXL 3.0 引入了多層交換,支持交換結構的實施。CXL 2.0 支持單層交換。借助 CXL 3.0,啓用了交換結構,其中交換機可以連接到其他交換機,從而大大增加了擴展的可能性。

第三,“按需”內存範例;

類似於拼車,CXL 2.0 和 3.0 在“按需”的基礎上爲主機分配內存,從而提供更高的內存利用率和效率。該架構提供了爲標稱工作負載(而不是最壞情況)配置服務器主內存的選項,能夠在需要時訪問池以處理高容量工作負載,並爲 TCO 帶來更多好處。最終,CXL 內存池模型可以支持向服務器分解和可組合性的根本轉變。在此範例中,可以按需組合離散的計算、內存和存儲單元,以有效地滿足任何工作負載的需求。

第四,完整性和數據加密 (IDE);

分解——或分離服務器架構的組件——增加了攻擊面。這正是 CXL 包含安全設計方法的原因。具體來說,所有三個 CXL 協議都通過完整性和數據加密 (IDE) 來保護,IDE 提供機密性、完整性和重放保護。IDE 在 CXL 主機和設備芯片中實例化的硬件級安全協議引擎中實現,以滿足 CXL 的高速數據速率要求,而不會引入額外的延遲。應該注意的是,CXL 芯片和系統本身需要防止篡改和網絡攻擊的保護措施。在 CXL 芯片中實現的硬件信任根可以爲安全啓動和安全固件下載的安全和支持要求提供此基礎。

第五,將信令擴展到 64 GT/s;

CXL 3.0 帶來了標准數據速率的階躍函數增加。如前所述,CXL 1.1 和 2.0 在其物理層使用 PCIe 5.0 電氣:32 GT/s 的 NRZ 信號。CXL 3.0 秉承了以廣泛採用的 PCIe 技術爲基礎構建的相同理念,並將其擴展到 2022 年初發布的最新 6.0 版 PCIe 標准。使用 PAM4 信號將 CXL 3.0 數據速率提高到 64 GT/s。我們涵蓋了 PCIe 6 中 PAM4 信令的詳細信息——您需要知道的一切。

得益於CXL的出現,开發者可以簡化和改進低延遲連接和內存一致性,顯著提高計算性能和效率,同時降低 TCO。此外,CXL 內存擴展功能可在當今服務器中的直接連接 DIMM 插槽之上實現額外的容量和帶寬。CXL 使得通過 CXL 連接設備向 CPU 主機處理器添加更多內存成爲可能。當與持久內存配對時,低延遲 CXL 鏈路允許 CPU 主機將此額外內存與 DRAM 內存結合使用。大容量工作負載的性能取決於大內存容量,例如 AI。考慮到這些是大多數企業和數據中心運營商正在投資的工作負載類型,CXL 的優勢顯而易見。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:CXL2.0DRAM,全球首款!

地址:https://www.breakthing.com/post/57948.html