“了解芯片簡史,你對中國半導體的未來如何看?”。走心評論互動轉發,挑選一位粉絲送出圖書《芯片簡史》一本。

and,2023年全景讀書會讀者粉絲群,交流讀書心得和互推薦書交流知識,有興趣請給公衆號後台私信你的微信號,並標注暗號:我要加入全景讀書會。

“

“爲什么是5000天?and本文摘取的凱文·凱利的40條未來,最觸動你的是哪條和說說理由”。走心評論互動轉發,挑選一位粉絲送出圖書《鮮活的經濟學》一本。

and,2023年全景讀書會讀者粉絲群,交流讀書心得和互推薦書交流知識,有興趣請給公衆號後台私信你的微信號,並標注暗號:我要加入全景讀書會。

是哪條和說說理由”。走心評論互動轉發,挑選一位粉絲送出圖書《鮮活的經濟學》一本。

and,2023年全景讀書會讀者粉絲群,交流讀書心得和互推薦書交流知識,有興趣請給公衆號後台私信你的微信號,並標注暗號:我要加入全景讀書會。

如果把晶體管比作糧食,我們可以參考解決糧食危機的方法,來說明應對芯片挑战的三種思路。

第一,最直接的就是繼續提升主要糧食的單位面積產量,這對應於提高芯片中晶體管的密度,這被稱爲“延續摩爾”(More Moore)。 第二,是擴展其他糧食種類,提高豐富程度,這意味着除了CPU、內存等數字芯片之外,還要大力拓展模擬、射頻、電源、顯示、柔性芯片等的用途,以及通過3D芯片將各種功能集成在一起,這叫作“擴展摩爾”(Morethan Moore)。 第三,也是最長遠的,是开發全新的糧食品種,這對應於探索MOS場效晶體管以外的新型晶體管,例如碳納米管場效晶體管(簡稱CNTFET或CNFET)、阻變式存儲器(簡稱RRAM)、相變隨機存取存儲器(簡稱PCRAM)、隧穿場效晶體管(簡稱TFET)等,這條路徑叫作“超越摩爾”(Beyond Moore)。

01

“延續摩爾”

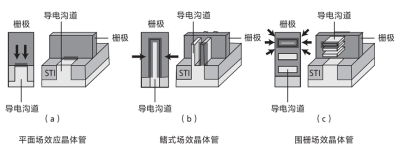

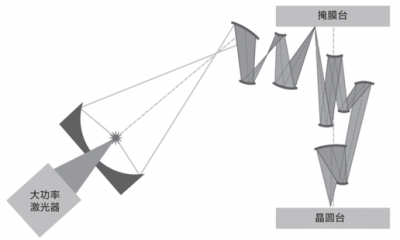

半導體業界繼續縮小晶體管尺寸,提高芯片裏晶體管的密度,是“延續摩爾”路徑的主要目標。 當工藝節點從5納米進到3納米和2納米時,FinFET遇到了一個老問題,晶體管無法有效關斷,漏電流飆升導致發熱嚴重。盡管FinFET已經變成了立體結構,可通過凸起的三個側面去關斷導電溝道,但仍無法完全關斷。 2003年,研究人員提出了更大膽的“納米线”(Nano-wire)結構。在這種結構中,晶體管的導電溝道變成納米粗細的一根“线”,完全被一個環形的“柵”給全方位地環繞,就好像一只“手”握着橡皮水管。在“手”上施加電壓,能更好地關閉晶體管,減小漏電流。 雖然這種結構解決了晶體管關斷的問題,但也對晶體管开啓後通過的電流大小造成了影響:細細的納米线對電流的阻礙作用極大。 爲此,2006年法國原子能委員會電子與信息技術實驗室(CEA-Leti)的研究人員提出納米片(Nano-sheet)結構。這類晶體管又叫GAAFET(見圖14-3)。在這種結構中,連接晶體管开關兩側的不再是細細的“线”,而是薄而寬的“片”,這樣全包圍的結構更利於關斷晶體管,而多個薄而寬的片又提升了導電能力。2017年,IBM公司展示了這種堆疊的納米片晶體管。2021年5月,IBM公司採用納米片成功突破2納米技術節點,在一個指甲蓋大小的芯片上集成了500億個晶體管。

02

“擴展摩爾”

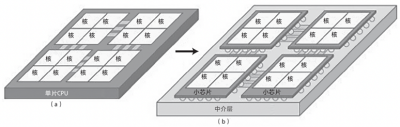

隨着“延續摩爾”遇到的障礙越來越大,人們开始尋找其他解決路徑。2005年,ITRS提出了“擴展摩爾”的概念。這條路徑追求的不是縮小單個晶體管的尺寸,而是增加系統功能的多樣性,在一個芯片上集成和實現豐富的功能。 這條路徑關注的不是CPU和存儲器這些需要最先進工藝的數字芯片,而是模擬、功率、傳感以及數模混合芯片,它們不需要最小的晶體管,但能實現豐富的應用場景。 “擴展摩爾”根據頂層的應用與需求來拉動技術的發展,其中一個最大的需求就是物聯網。過去幾十年中,個人電腦和手機先後普及,但數量已經趨近飽和,將來的數量至多再提高3倍。而未來的物聯網設備,包括智能家居、健康監測、自動駕駛汽車、環境監測等,還會增加3個數量級,構成一個無處不在的物聯網世界。 例如,自動駕駛汽車裏需要激光測距雷達、超聲波傳感器、加速度計等多種傳感器;醫療領域需要可穿戴式的生理信號監測設備,以及爲了抑制癲癇發作的植入式傳感器和電流刺激芯片等;環境監測領域需要能探測各種二氧化碳、硫化物等污染物的傳感器芯片。這些傳感器需要跟CPU、存儲器等集成在一起,從而實現豐富的功能。 此外,我們也需要高效的電源,想要實現極低的功耗,滿足便攜或移動設備的要求。我們同樣需要用高信噪比的傳感器和模擬電路來感知或採集微弱的生理信號、危險氣體的濃度等。我們也需要滿足各種頻段的無线射頻電路,實現更多樣的無线連接。 另外一個有“擴展摩爾”需求的是能源領域。與硅相比,氮化鎵和碳化硅等半導體材料的性能更優異,用它們制成的功率器件可以在相同的耐受電壓下提供更高的开關頻率,或者在相同的耐受電壓和开關頻率下有更低的導通和开關損耗。 此外,人們也將對能量收集技術產生極大的需求,因爲許多傳感器安置在露天環境中,沒有市電供電,也不方便更換電池。而能量收集的途徑可以是機械振動、冷熱溫差或者無线電波、光线等,這將大大地延長芯片的工作時長。 最後,柔性電子將在基於織物的可穿戴設備、折疊屏幕、薄膜太陽能電池等方面發揮作用。未來相當一部分柔性電子設備將通過打印在柔性基材上的方式制造出來,但這需要業界在有機材料和碳基材料上取得進一步突破。 從2017年开始,一種叫作小芯片(Chiplet)的技術引起了業界,尤其是超威半導體公司的興趣。以往,人們盡量將不同的電路模塊集成到一顆芯片上,以降低成本。但是人們發現,加工的芯片面積越大,芯片良率(晶圓片上性能良好的裸芯片的比率)越低,進而推高了成本。反之,將大芯片拆成小芯片則能提高良率,降低成本。 於是,一種相反的趨勢出現了:將大芯片拆解成尺寸較小的單個芯片,分別制造,然後再通過封裝技術合成在一起(見圖14-5)。這有點像先制造小塊的樂高積木,然後將其拼成一個更大的整體。例如,將一顆面積爲360平方毫米的芯片拆成4顆小芯片分別制成,它的良率將提高兩倍多。在這一趨勢下,未來CPU中的內核會越來越多。超威半導體公司的一款“霄龍”處理器(簡稱EPYC)中有8個小芯片,每個小芯片中又有8個內核,總共有多達64個內核。

03

“超越摩爾”

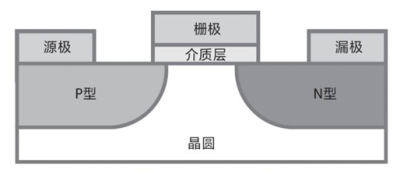

大數據、物聯網、人工智能和超級計算等新技術的計算需求對芯片性能和能效提出了更高的要求,於是就有了第三條路:“超越摩爾”,又叫“超越CMOS”,即在主流的CMOS技術之外尋找更好的可能。 硅晶體管中的漏電流一直是科學家的心頭大患。爲此,人們發明了TFET(其結構見圖14-6)。它利用導帶與價帶之間的量子隧穿效應,控制晶體管的开與關,使漏電流更小、導通電流更大,突破了傳統晶體管中的麥克斯韋-玻爾茲曼統計限制,使得亞閾值擺幅低於60mV/dec的下限。不過,TFET的源極與漏極不再像MOS場效晶體管那樣同爲P型半導體或同爲N型半導體,而是一邊爲P型半導體,另一邊爲N型半導體,這對器件制造和應用提出了新的挑战。 圖14-6 TFET的結構 硅材料雖然適合大規模生產,儲藏豐富,還有一個天然穩定的絕緣氧化層,但它也有難以克服的缺點:電子遷移率低,導致开關速度不高;散熱特性一般,限制了芯片的工作頻率。這些問題都讓“延續摩爾”之路變得困難重重。 而碳材料則在遷移率、小尺寸和散熱特性方面具有優勢。在實驗室中,研究者已經用碳納米管制成了CNTFET(見圖14-7),結構類似於硅MOS場效晶體管,只是將中間的導電溝道換成遷移率更好、散熱性更好、尺寸更小的碳納米管。目前,人們仍在解決大規模制備方面的挑战。

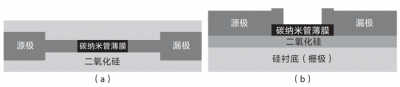

圖14-6 TFET的結構 硅材料雖然適合大規模生產,儲藏豐富,還有一個天然穩定的絕緣氧化層,但它也有難以克服的缺點:電子遷移率低,導致开關速度不高;散熱特性一般,限制了芯片的工作頻率。這些問題都讓“延續摩爾”之路變得困難重重。 而碳材料則在遷移率、小尺寸和散熱特性方面具有優勢。在實驗室中,研究者已經用碳納米管制成了CNTFET(見圖14-7),結構類似於硅MOS場效晶體管,只是將中間的導電溝道換成遷移率更好、散熱性更好、尺寸更小的碳納米管。目前,人們仍在解決大規模制備方面的挑战。

圖14-7 CNTFET

注:俯視圖(a)和側視圖(b)。 無論是BJT,還是MOS場效晶體管等器件,都是用電子作爲信息處理的媒介,創新的思路則是採用速度更快的光子。光子沒有散熱問題,不受電子噪聲影響,而且光信號延遲小、通信帶寬遠高於電信號。此外,用硅材料就能做出各種光處理器件(光波導、光濾波器和光連接器等),它們很容易就能集成到CMOS芯片中,從而大大地降低成本。制造光互連處理器已經开始變得可能。不過,硅光電子仍需要突破一些技術瓶頸才能進入實際應用。 不過,“危”中藏“機”。此前業界的絕大部分經費和人力都投到了硅MOS場效晶體管器件的相關研究中,以維持其按照摩爾定律預測的速度前進。現在,MOS場效晶體管尺寸縮小之路的結束將爲非MOS場效晶體管器件的發展讓出一條路。 在芯片設計的EDA領域,隨着芯片中數字、模擬、射頻等電路融合在一個系統中,電磁幹擾將更加復雜,散熱問題與性能退化需要更小心地應對,不同電路之間的接口也變得更加復雜。最近幾年,人工智能开始用於解決芯片布线問題,以尋找最優解。 在應用層面,爲了滿足不同場景下的計算需求,人們正在研究高帶寬存儲器(簡稱HBM)、存內計算、近存計算、神經形態計算、近似計算和集感存算爲一體的芯片技術。 這些設想將來都能實現嗎?我們目前還無法確知,但它們未來一定會以一種我們從未看到過、聽到過,甚至從未想象過的方式出現,打破我們曾深信不疑的論斷。也許這裏應借用計算機科學家艾倫·凱(Alan Kay)說過的一句話來回答:“預測未來最好的方式就是把它發明出來。” 了解更多

了解更多

內容簡介:

一本聚焦熱門話題、熱門行業的實力之作,完整呈現芯片發明和發展的60多年歷程。

全書完整呈現了芯片發明與發展的歷程,從支撐芯片產業發展的量子力學講起,逐漸發展到半導體物理學,進而催生了半導體器件,這些器件又由簡到繁,像一顆發芽的種子,演化出了雙ji型晶體管、MOS場效晶體管、光電二ji管等,並由此集成構造出了模擬芯片(通信和傳感器芯片等)、數字芯片(CPU、存儲器、FPGA等)和光電芯片等。蕞後,本書還展示了芯片設計方法和制造方法由手工到自動的發展過程,並指出了芯片未來面對的挑战和可能的解決路徑。可以說,了解芯片,有這一本書就夠了。

作者:資深芯片研究專家。早年留學法國,獲法國裏昂國立應用科學學院集成電路碩士學位和利摩日大學高頻微電子學博士學位,分別在華爲公司、法國裏昂納米國家實驗室和北京大學深圳研究生院從事集成電路設計的教學與科研工作,積累了二十余年經驗。

歡迎轉發評論留言,還有贈書福利和更多好書等着你

本文僅代表作者個人觀點,不代表本公衆號立場。本公衆號轉載此圖文僅出於傳播更多資訊之目的。如有侵權或違規請及時聯系我們,我們將立刻予以刪除。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:半導體產業面臨的挑战日益嚴峻,我們該如何應對?|全景讀書會(互動有禮)

地址:https://www.breakthing.com/post/69225.html