來源:內容由半導體行業觀察

編譯自eenewsanalog

據路透社報道,芯片制造商英特爾和意大利政府已選擇意大利北部維羅納附近的維加西奧作爲價值 45 億歐元的chiplet組裝廠的選址。

預計羅馬政府將通過向英特爾提供公共資金和關於勞動力和能源成本的特殊條款來提供高達 40% 的投資。組裝廠的運營預計將在 2025 年至 2027 年之間的某個時間點开始。

幾個月來,英特爾一直在與意大利政府就一項將直接創造 1500 個工作崗位並在供應鏈中創造 3500 個工作崗位的協議進行談判。

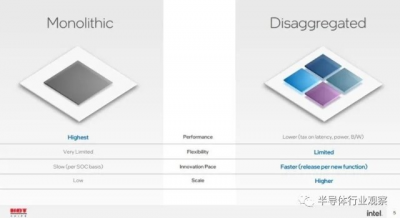

chiplet組裝是指從多個芯片制造組件,以便每個都可以在最適合其功能的半導體工藝中制造。這將允許存儲器、數字邏輯、模擬、RF 和 I/O 電路以 3D 排列方式組裝。然而,這種新穎的制造方式主要用於高性能計算,尚未成爲主流。隨着標准化程度的提高,它可能开始在汽車和工業電子等領域得到應用。

此舉是英特爾承諾未來幾年在歐洲投資 800 億歐元(約合 800 億美元)的一部分。該公司已承諾斥資 170 億歐元在德國馬格德堡建造兩座晶圓廠,以對其在愛爾蘭萊克斯利普的現有晶圓廠進行大量投資,並正在收購與意法半導體共享晶圓廠的 Tower Semiconductor。

路透社稱,Vigasio 是兩個候選地址中的首選。另一個位於皮埃蒙特地區西北部。Vigasio 的優勢之一是它與德國馬格德堡的公路和鐵路連接良好。報告稱,他們已考慮在倫巴第大區、普利亞大區和西西裏島進行其他選址。

英特爾眼裏的Chiplet未來

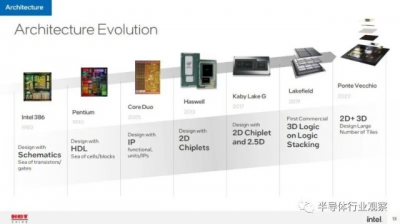

這是基於英特爾關於Meteor Lake及其客戶端策略的 Hot Chips 34 演講的第二篇文章。我們已經介紹了 Meteor Lake,所以這將是一篇關於分類未來的更大的文章。毫無疑問,這是芯片設計的新時代。

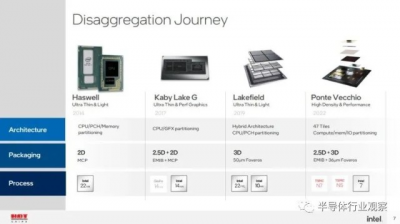

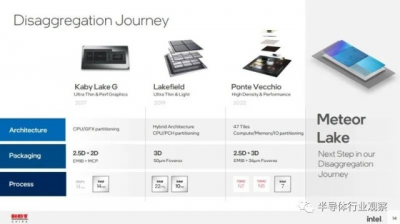

在 Hot Chips 34 (2022) 上,英特爾討論了其從爲當今大部分細分市場生產的單片芯片到分類未來的歷程。

英特爾聯合封裝芯片已有一段時間了。英特爾 Ponte Vecchio可能是該公司將 47 個不同的tile集成在一個封裝中的最佳示例。目前,高端 GPU 可能支持這一點,但在 ASP 低得多的客戶端空間中也可能過於復雜。

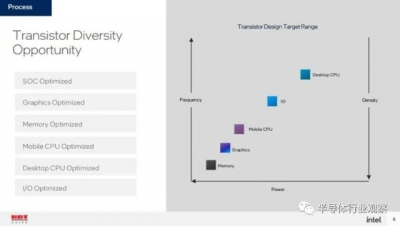

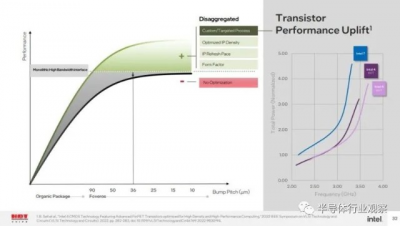

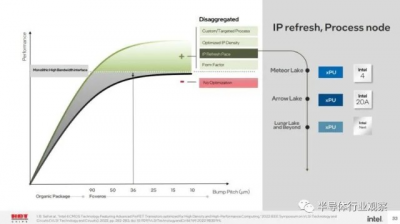

自從英特爾开始公开採用平鋪方法以來,英特爾在消息傳遞方面一直保持一致的一項內容是,不同的晶體管在不同的工藝上以最佳方式工作。轉向tile允許英特爾匹配晶體管類型以進行處理。

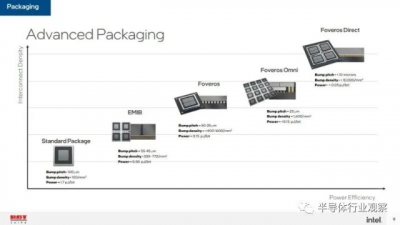

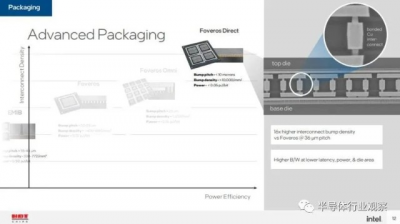

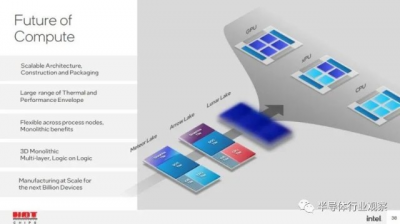

英特爾還擁有一條跨越 2D 技術和 3D 技術的封裝线,例如其 Foveros 线。

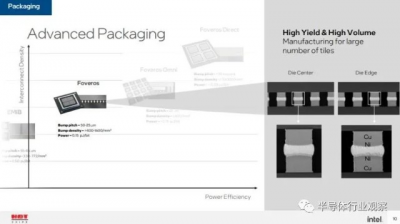

在tile中制造消費類設備的部分挑战是英特爾需要大規模制造。這意味着英特爾需要有一個實施成本相對較低的工藝。Foveros 是英特爾在其大部分下一代產品組合中使用的一系列技術。

英特爾有許多代的 Foveros 技術,他們自2018 年架構日討論以來一直在討論組合個技術的發展。

下一代爲連接提供了更高的密度,但也降低了通過位的功耗。這一點至關重要,因爲在多芯片解決方案中,每比特傳輸的功率(通常表示爲 pJ/bit)可能是一筆巨大的成本。省電傳輸數據是可以重新用於工作的電源。在現代系統中,我們經常會聽到這樣的軼事,即通過系統移動數據的能力大於用於做有用工作的能力。

雖然 Ponte Vecchio 是我們所看到的處理器的當前高水位线,但英特爾正在爲其客戶端芯片轉向類似但按比例縮小的方法。

雖然我們已經介紹了 Meteor Lake,但我們將使用幻燈片作爲正在發生的事情的示例。

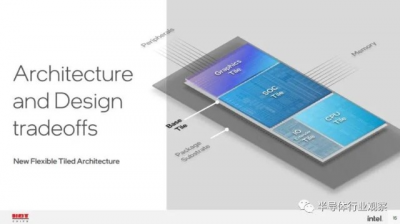

英特爾有一個基礎tile,可將電源和數據連接傳送到上面工作的tile。

通過更改爲使用此基礎芯片的平鋪方法,需要權衡取舍。人們提到的第一個是成本。英特爾表示,添加基礎裸片的成本被能夠使用與最高效工藝對齊的較小裸片所節省的成本所抵消。在 CPU 競爭價格可能有 10 到 20 美元增量的客戶空間中,以這種方式制造芯片增加 100 美元是不可行的。

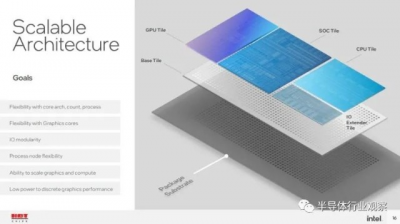

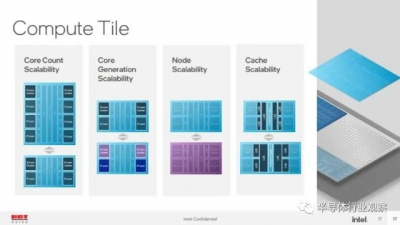

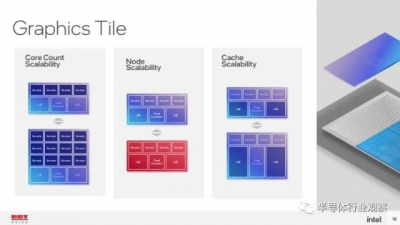

通過這種方法,英特爾可以設計不同的計算單元。有些可能有不同的核心數量和核心類型。這些圖塊也可以有不同的緩存。緩存佔用了圖塊上的大量區域。擁有一個與設備其余部分具有相對標准接口的計算塊意味着英特爾可以在新一代內核或新一代工藝節點上進行創新,然後輕松地將它們集成到現有產品中。

圖形單元可以類似地隨着時間而修改。

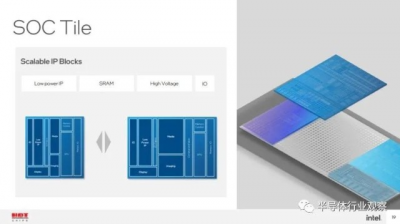

SoC 單元很有趣,因爲英特爾表示顯示、成像和媒體比 GPU 單元更適合這個單元。英特爾沒有說的是,一旦有硬件加速器,或者有可能有四個輸出的顯示器,那么這不一定需要每一代都改變。將跨越多代的功能引入 SoC 意味着英特爾可以集中精力修改 CPU 和 GPU 塊,而無需驗證顯示功能是否適用於未來 GPU 用作示例的新制程節點。

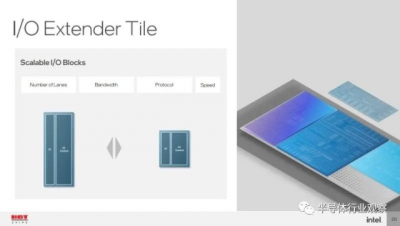

I/O 擴展塊可以是很多東西。除了 Meteor Lake 之外,PCIe 通道、USB 通道等功能可以分解成塊然後集成。

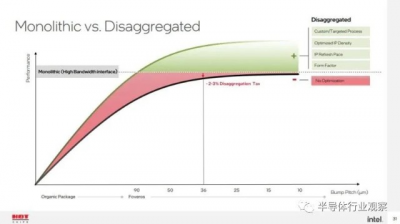

這正是英特爾進行成本討論的地方。如前所述,在分解方面存在“稅”,但英特爾認爲它相對較小。

英特爾還認爲,通過能夠針對不同類型的tile針對不同類型的工藝節點,這將有助於抵消分類稅。

英特爾還認爲,能夠更快地利用新晶體管,也有助於抵消分類稅。

我們將在這裏很快注意到,這是一個 36 微米的凸塊間距。在 25 微米的 Foveros Direct 水平上,這種分解影響會更小。鑑於此,英特爾沒有詳細說明 Lunar Lake,但其圖表顯示了 Arrow Lake CPU/GPU tile刷新,同時保留了 SoC 和 I/O tile。Lunar Lake 有所不同,但也許英特爾已經向我們展示了未來。

兩年前,我們介紹了 SoC 容器化未來的英特爾方法。就像單體應用如何遷移到微服務一樣,英特爾正在從單體芯片轉向更小的塊。Meteor Lake/Arrow Lake 看起來很像 2020 年“IP/SOC Methodology Change”時代“Multiple Dies”的演變。CPU 是它自己的 tile,GPU 是它自己的 tile,但 I/O tile 已被分成兩部分。

英特爾討論的下一個演變是將事物分解爲單個 IP。然後它可以制造更小的小芯片。通過這樣做,它可以在每個 IP 上更快地進行創新。然後,英特爾的產品組需要採用 IP 塊,並根據這些 IP 塊爲不同的細分市場組合芯片。

也許更有趣的方面不僅僅是英特爾在上面展示的內容,而是更進一步,看看它的集成工作。該公司發布了 UCIe,該行業正迅速受到關注,以促進小芯片生態系統的發展。

這帶來的影響是巨大的。對於消費領域,我們是否會看到更多與 CPU 封裝的集成,因爲通過 I/O tile添加 I/O(例如更高速的網絡、人工智能加速或更多?)在英特爾的產品組合中,這是否意味着Dell Core i9 與 HP 或 Lenovo 的 tile 集成了不同的硅片?

不僅限於供應商本身,這對英特爾未來的運營方式有着巨大的影響。轉向平鋪方法可能意味着英特爾實際上可以制作高度差異化的解決方案。產品經理不必採用基於消費內核的芯片,然後指定 ECC,並爲 Xeon E 系列提供速度和內核數量組合,也許可以選擇 P-tiles、E-tiles 、AI-tiles、networking tiles、I/O tiles,所有這些都可能不是來自英特爾。這與產品團隊過去實際完成的任務截然不同。

對於市場來說,這將帶來新的動力。VPN 設備供應商可能能夠獲得僅爲其機器集成的自定義加密小芯片。HPE 和 Dell EMC 服務器可能使用不同類型的 Xeon。也許戴爾酷睿 i7 將不再在華碩酷睿 i7 中工作(這已經發生在AMD PSB上。)對於 I/O 芯片上的加速器是否有市場特定的要求,使芯片像藍光一樣具有特定的區域?

雖然英特爾的 Hot Chips 34 演講集中在其客戶端 Meteor Lake 解決方案上,但更具影響力的含義可能是它對英特爾、業內其他公司和英特爾客戶的意義。如果一個真正的小芯片市場發展起來,那么我們獲得新創新的速度就會加快。它還可能給我們過去十年或兩年所擁有的大部分結構化市場造成混亂。

來個【點贊、分享、在看】

一鍵三連

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:英特爾:意大利建Chiplet工廠

地址:https://www.breakthing.com/post/20854.html