幾十年來,摩爾定律推動了半導體行業的進步。然而,在過去 10 年中,包括 NVIDIA 首席執行官黃仁勳在內的一些行業領導者認爲 “摩爾定律已死”。

現在,制造商和研究人員正在研究擴大半導體規模和提高性能的新方法。一家初創公司NeoLogic正在採用一種獨特的方法來應對這一挑战,採用“VLSI 設計的新範式”。

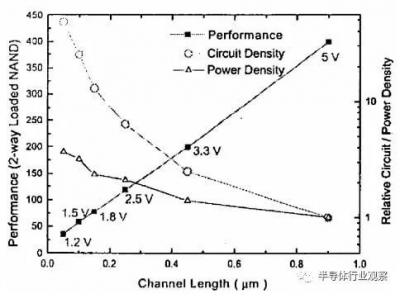

摩爾定律依賴於制造努力將晶體管柵極長度每代降低 0.7 倍。減小晶體管柵極長度會產生許多重要的好處:它可以降低電路成本、降低功耗、提高性能並增加晶體管數量。

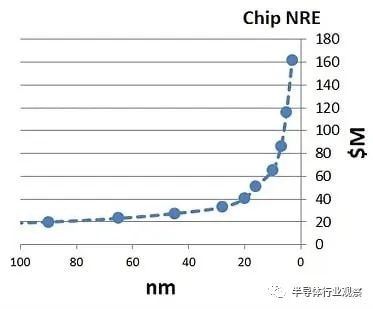

然而,隨着微縮一直持續到 5nm 及以下領域,微縮可能會帶來比其解決的問題更多的問題。

這些問題之一是電路復雜性。隨着更多晶體管被添加到相同面積的芯片中,設計變得更加密集和復雜,需要精心設計的電源、時鐘以及全局和本地信號傳輸方案。最終,這種復雜性成爲限制小型晶體管規模化以及規模化實現多少性能的限制因素。

另一個挑战是功率密度。在更小的區域內使用更多的晶體管,單位面積消耗的功率會顯着增加。由於高電路熱量,這會導致設計可靠性問題。

爲了應對這些挑战,初創公司 NeoLogic 設計了一個獨特的解決方案。

NeoLogic由幾位半導體和 VLSI 專家創立,完全超越 CMOS 設計。相反,NeoLogic 使用其專利准 CMOS 技術(稱爲 NeoMOS)設計 VLSI IP。

雖然 NeoLogic 沒有透露其 NeoMOS IP 的許多細節,但該公司解釋說,准 CMOS 架構將單晶體管邏輯(即 nMOS 或 pMOS)與 CMOS 邏輯集成在一起,以創建邏輯門和電路。據該公司稱,添加單晶體管邏輯可顯着減少 VLSI 設計中的晶體管數量。

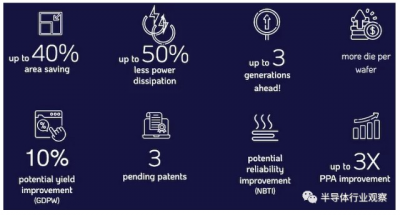

NeoLogic 聲稱,NeoMOS 的好處包括降低成本、面積、功耗和設計復雜性。與標准 CMOS 產品相比,據說 NeoMOS 可降低 50% 的功耗並減少 40% 的面積,同時保持或改善電路延遲。NeoLogic 表示,這相當於每瓦性能提高了 3 倍,並使公司能夠有效地跨越三代節點。

按照目前的情況,NeoLogic 通過許可協議銷售其 IP 塊,但有一天該公司希望銷售自己的處理器和其他基於 NeoMOS 技術的技術。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:初創公司,用新型晶體管延續摩爾定律

地址:https://www.breakthing.com/post/25831.html