來源:內容由半導體行業觀察編譯自semiwiki,謝謝。

TSMC 的 3DFabric計劃理應成爲他們研討會的一大焦點。我記得當台積電首次公开 CoWos 半導體生態系統時,包括我在內的所有人都嘆了口氣,想知道爲什么台積電要冒險進入利潤率相對較低的封裝領域。

現在我們知道爲什么了,這絕對很棒!

2012 年,台積電與賽靈思一起推出了當時最大的 FPGA,由四個相同的 28 納米 FPGA 片組成,並排安裝在硅中介層上。他們還开發了硅通孔 (TSV)、微凸塊和重新分布層 (RDL) 來互連這些構建塊。根據其結構,台積電將這種 IC 封裝解決方案命名爲 Chip-on-Wafer-on-Substrate ( CoWoS )。

這種基於構建塊和 EDA 支持的封裝技術已經成爲高性能和高功率設計的事實上的行業標准。中介層最多可達三個步進電機區域(three stepper fields large),允許並排組合多個裸片、裸片堆疊和無源元件,並與亞微米 RDL 互連。最常見的應用是 CPU/GPU/TPU 與一個或多個高帶寬存儲器 (HBM) 的組合。

2017 年,台積電宣布了集成扇出技術 ( InFO )。它使用聚酰胺薄膜代替 CoWoS 中的硅中介層,從而降低單位成本和封裝高度,這兩個都是移動應用的重要成功標准。台積電已經出貨了數千萬個用於智能手機的 InFO 設計。

2019 年,台積電推出了集成芯片系統 ( SoIC ) 技術。使用前端(晶圓廠)設備,台積電可以非常精確地對齊,然後使用許多窄間距銅焊盤進行壓焊設計,以進一步最小化外形尺寸、互連電容和功率。

今天,台積電擁有 3DFabric,這是一個全面的 3D 硅堆疊和先進封裝技術系列。以下是媒體發布會上的台積電相關成果:

TSMC 3DFabric 包含多種先進的 3D 硅堆疊和先進的封裝技術,可支持範圍廣泛的下一代產品:

在 3D 硅堆疊部分,台積電正在 TSMC-SoIC 系列中添加基於微凸點的 SoIC-P,以支持更多對成本敏感的應用。

2.5D CoWoS 平台可爲人工智能、機器學習和數據中心等 HPC 應用集成高級邏輯和高帶寬內存。InFO PoP 和 InFO-3D 支持移動應用,InFO-2.5D 支持 HPC chiplet 集成。

SoIC 堆疊芯片可以集成到 InFO 或 CoWoS 封裝中,以實現最終系統集成。

CoWoS家族

主要針對需要集成高級邏輯和 HBM 的 HPC 應用程序。

TSMC 已支持來自超過25 個領域的140 多種CoWoS 產品

所有 CoWoS 解決方案的中介層尺寸都在增加,因此它們可以集成更先進的硅芯片和 HBM 堆棧,以滿足更高的性能要求。

台積電正在开發一種 CoWoS 解決方案,該解決方案具有高達6 倍光罩尺寸(約 5,000 平方毫米)的 RDL 中介層,能夠容納 12 個 HBM 存儲器堆棧。

InFO技術

對於移動應用,自 2016 年以來,InFO PoP 一直在爲高端移動設備量產,並且可以在更小的封裝尺寸中容納更大、更厚的 SoC 芯片。

對於 HPC 應用,無基板 InFO_M 支持高達 500 平方毫米的小芯片集成,適用於對外形尺寸敏感的應用。

3D硅堆疊技術

SoIC-P 基於 18-25m 間距 bump 堆疊,適用於對成本更敏感的應用,如移動、物聯網、客戶端等。

SoIC-X 基於無擾動堆疊,主要針對 HPC 應用。其晶圓上芯片堆疊方案具有 4.5 至 9m 鍵距,並已在 TSMC 用於 HPC 應用的 N7 技術上量產。

SoIC 堆疊芯片可以進一步集成到 CoWoS、InFo 或傳統的倒裝芯片封裝中,用於客戶的最終產品。

3DFabric 聯盟和 3Dblox 標准

在去年的开放式創新平台(OIP) 論壇上,台積電宣布成立新的 3DFabric聯盟,這是繼 IP、EDA、DCA、Cloud 和 VCA 聯盟之後的第六個 OIP 聯盟,以促進下一代 HPC 和移動設計的生態系統協作:

提供 3Dblox 开放標准,

實現內存和 TSMC 邏輯之間的緊密協作

以及將 Substrate 和測試合作夥伴引入生態系統。

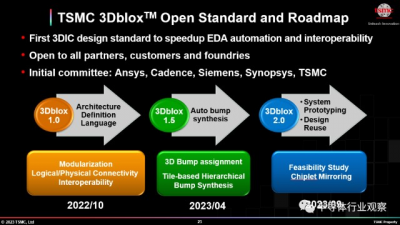

TSMC 推出了 3Dblox 1.5,這是其开放標准設計語言的最新版本,旨在降低 3D IC 設計的門檻。

TSMC 3Dblox是業界首個加速 EDA 自動化和互操作性的 3D IC 設計標准。

3Dblox1.5 添加了自動凸點合成,幫助設計人員處理具有數千個凸點的大型芯片的復雜性,並有可能將設計時間縮短數月。

台積電正在开發 3Dblox 2.0,以實現系統原型設計和設計重用,目標是今年下半年。

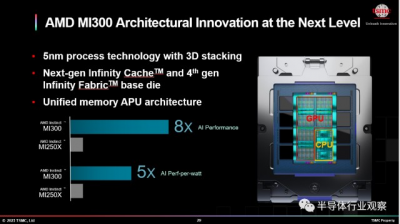

以上是台積電 3DFabric 技術如何啓用 HPC 芯片的示例。這也支持我的觀點,即 AMD 收購 Xilinx 的最大價值之一是 Xilinx 芯片團隊。絕對沒有人比 Xilinx 更了解如何實施先進的TSMC封裝解決方案。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電的先進封裝

地址:https://www.breakthing.com/post/55230.html