來源:內容由半導體行業觀察編譯自allaboutcircuit,謝謝。

爲了幫助設計人員快速採用他們的先進工藝,台積電 (TSMC) 最近爲針對其先進節點的 EDA 工具授予了一系列認證。

隨着 N3E、N4P 和 3DFabric 工藝的發布,新的獨特設計要求要求進行新的認證,以確保同時滿足設計人員的系統要求和 TSMC 的工藝要求,從而縮短上市時間。

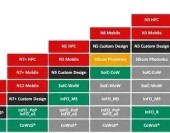

台積電設計解決方案隨着時間的推移而發展。隨着時間的流逝,提供了越來越多的技術來滿足各種設計需求。圖片由台積電提供。

在本文中,我們將簡要介紹台積電的先進工藝及其影響,然後概述台積電授予的認證以及這些認證如何幫助未來的設計人員。

保持進步

台積電延續了晶體管更小、更密集的趨勢,此前已宣布其最新的數字節點N3E 和 N4P,以使設計人員能夠跟上減小整體 IC 尺寸的步伐,爲相同尺寸的晶圓上的附加功能創造更多空間。這兩個節點都是現有技術的擴展,但與原始節點相比提供了增強的性能。

N3E技術是一種 3 納米“增強型”技術,與以前的技術相比,在速度和功耗方面都有了顯着提高。此外,根據 特徵尺寸以自定義方式實施 FinFET的自由度允許在速度、面積和效率方面進行最佳權衡。

N3E 工藝變化提供給設計人員以提高性能與功耗。圖片由台積電提供

N4P技術,4nm工藝,同樣是N4平台的延伸。附加一個“P”表示性能,與 N5 平台相比,N4P 工藝的性能提升 11%,比 N4 平台提升 6%。N4P 平台專爲輕松從基於 5 nm 的設計遷移而構建,使設計人員能夠幾乎輕松地提高其設計的性能。

最後,爲了避免摩爾定律的終結,台積電還爲其 3DFabric 工藝授予了認證:該技術旨在將 IC 設計領域從主要的平面視角轉變爲體積視角。使用 3DFabric,感興趣的設計人員可以爲他們的項目添加另一個維度,允許使用 TSMC 的 硅堆疊和先進封裝技術進行更廣泛的集成,同時保持目標板上相同的佔用面積。

爲工作找到合適的工具

盡管一些工程師可能相信他們設計工作電路的能力,但我們確實需要某種自動化或模擬來驗證復雜的設計。爲了確保 EDA 工具不僅滿足設計人員的需求,而且滿足工藝流程的需要,台積電成立 了 EDA 聯盟,直接與 EDA 工具供應商合作。

EDA聯盟共有16個合作夥伴,包括Cadence、Siemens、Ansys和Synopsys。這些小組中的每一個都提供自己的與 TSMC 工藝兼容的 EDA 工具,範圍從 物理驗證到 時序和功率籤核。爲了確保兼容性並縮短上市時間,台積電已發布認證,以向設計人員保證他們的 EDA 工具符合台積電的內部要求。

截至 2022 年 10 月 26 日的 3DFabric EDA 工具認證狀態。圖片由 台積電提供。

台積電主要專注於爲其高級節點 N3E、 N4P和 3DFabric頒發認證。根據具體應用,某些 EDA 工具可能會提供改進的功能或更好的性能。盡管 EDA 工具的產品數量衆多,但設計人員可以放心,只要他們想要的工具經過認證,就可以保證與 TSMC 的高級節點一起工作。

對您的定制設計充滿信心

隨着摩爾定律不可避免的終結比以往任何時候都更接近,高性能的先進節點和新的設計方法(如 3D 集成)變得比以往任何時候都更加重要。然而,如果沒有適當的 EDA 支持,設計師的工作就會變得越來越困難。

台積電开創的直接與 EDA 公司合作的先例標志着自上而下的支持網絡設計領域的一個有利趨勢,減少了 EDA 工具的开發時間,並允許設計人員在沒有擔心他們沒有合適的工具。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電3nm工藝,再進一步

地址:https://www.breakthing.com/post/28390.html