隨着AI、5G和其他先進制程技術的發展,全世界正透過智慧邊緣網絡產生大量的運算工作負載,需要更快、更節能的芯片來滿足此需求。

預計到2030年,因需求激增,全球半導體市場約1兆美元,其中高效能運算(HPC)相關應用佔40%、智能型手機佔30%、汽車佔15%、物聯網佔10%。- 台積公司與其合作夥伴在2022年共創造了超過12,000種創新產品,運用近300種不同的台積公司技術。

台積公司持續投資先進邏輯制程、3DFabric和特殊制程等技術,以在適當的時間提供合適的技術,協助推動客戶創新。隨着我們的先進制程技術從10納米推進至2納米,我們的能源效率在約十年間以15%的年復合成長率增加,以支持半導體產業的驚人成長。

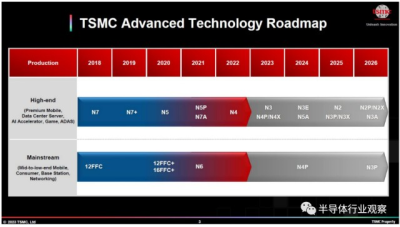

台積公司先進制程技術的產能年復合成長率在2019年至2023年間將超過40%。作爲第一家於2020年开始量產N5的晶圓廠,台積公司透過推出N4、N4P、N4X和N5A等技術,持續強化其5納米家族。台積公司的3納米制程技術是半導體產業中第一個實現高量產和高良率的制程技術,我們預計N3將在行動和HPC應用的驅動下實現快速且順暢的產能提升(ramping)。

此外,爲了進一步推展微縮,以在單體式系統單芯片(monolithic SoCs)中實 現更小且更優異的晶體管,台積公司亦在开發3DFabric技術,發揮異質整合的優勢,將系統中的晶體管數量提高5倍,甚至更多。

從2017年到2022年,台積公司對特殊制程技術投資的年復合成長率超過40%。到2026年,台積公司預計將特殊制程產能提升近50%

先進邏輯制程

2 納米家族

N2計劃於2025年量產;N2P和N2X則計劃在2026年推出。

納米片晶體管的效能已超過台積公司技術目標的80%,同時展示了優異的能源效率和更低的工作電壓(Vmin),非常適合作爲半導體產業節能運算的典範。作爲台積公司 N2制程技術平台的一部分,背面電軌(backside power rail)的設計爲其基线技術提供了額外的速度和密度提升。背面電軌設計最適合用於HPC產品,將於2025年下半年推出。透過減少壓降(IR drop)和訊號電阻-電容延遲(signal RC delays),使速度提升超過10-12%。由於晶圓正面擁有更多的布线資源,使得邏輯面積可減少10-15%。

3 納米家族

N3是台積公司目前最先進的邏輯制程技術,已依計劃在2022年第四季進入量產;N3E計劃在N3量產後一年推出,且已通過技術驗證,達成效能與良率目標。與N5相比,N3E在相同功耗下速度加快18%,在相同速度下功耗降低32%,邏輯密度提升約60%、芯片密度提升約30%。o N3E已經收到了第一批客戶產品設計定案(product tape-outs),並將在2023年下半年开始量產。

台積公司亦推出N3P和N3X來提升制程技術價值,在提供額外效能和面積優勢的同時,亦保持與N3E的設計規則兼容性,以最大程度地實現IP重復使用。在邁入量產的前三年,N3和N3E的新產品設計定案數量將是N5同時期的1.5至2倍,主要歸功於台積公司的技術差異化和准備就緒程度。

在保持與 N3E 設計規則兼容性的同時,提供額外的效能和面積優勢,以最大程度地實現 IP 重復使用。N3P 預計於 2024 年下半年开始量產,客戶可以在相同漏電下,速度增快 5%;在相同速度下,功耗降低 5-10%,以及與 N3E相比芯片密度增加 4%。o N3X:專爲 HPC 應用所設計,提供額外的最大震蕩頻率(Fmax),以在適度的漏電平衡下提高驅動效能(overdrive performance),這意味着相較於 N3P,N3X 在驅動電壓 1.2 伏特下,速度增快 5%,並擁有相同的芯片密度提升幅度。N3X 預計於 2025 年進入量產。

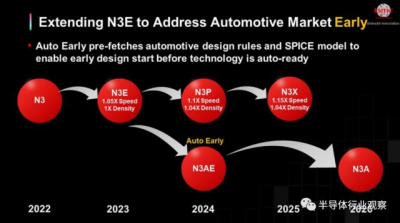

台積公司今日推出業界第一個基於 3 納米的 Auto Early 技術,命名爲 N3AE。N3AE 提供以 N3E 爲基礎的汽車制程設計套件(PDK),讓客戶能夠提早採用 3 納米技術來設計汽車應用產品,以便於 2025 年及時採用屆時已全面通過汽車制程驗證的 N3A 制程。

5 納米家族:

隨着台積公司5納米制程進入量產,所累積的經驗使得該制程的良率和效能不斷提升。在4 年間,與 N5 量產第一年相比,台積公司將該制程的效能提升高達17%、芯片密度增加 6%,並維持着相同的設計規則兼容性,以盡可能增加現有客戶設計的再利用。盡管N5需求強勁,N4P將自2024年推動需求進一步增加。與2022年相比,此一需求增加主要來自人工智能、網絡和汽車產品,這與產業趨勢密切相關。

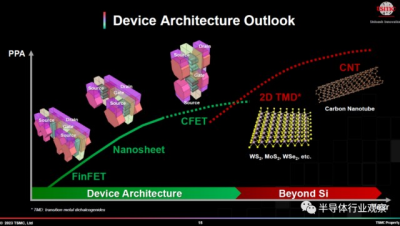

超越 N2 的技術創新

晶體管架構從平面式發展到FinFET,並即將轉變至納米片(nanosheet)架構。在納米片之後,台積公司認爲垂直堆棧的NMOS和PMOS(即互補式場效晶體管 CFET)是未來制程架構選項之一。

台積公司預估,在考量布线和制程復雜性後,芯片密度將可提升1.5至2倍。除了CFET,台積公司在低維材料(如碳納米管和2D材料)方面取得了突破,可能實現進一步的尺寸和能源微縮。

TSMC 3DFabric技術

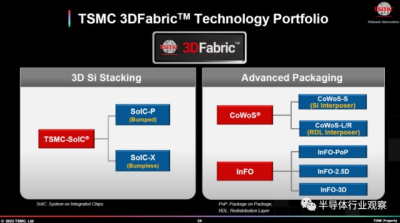

台積公司 3DFabric 系統整合技術包含各種先進的 3D 硅堆棧和先進封裝技術,以支援廣泛的次世代產品:

在 3D 硅堆棧方面,台積公司正於系統整合芯片(TSMC-SoIC )家族中加入微凸塊的 SoIC-P,以支援更具成本敏感度的應用。2.5D CoWoS 平台得以實現先進邏輯和高頻寬存儲器的整合,適用於人工智能、機器學習和資料中心等 HPC 應用;整合型扇出層疊封裝技術(InFO PoP)和 InFO-3D 支援行動應用,InFO-2.5D 則支援 HPC 小芯片整合。系統整合芯片(SoIC)堆棧芯片可被整合於整合型扇出(InFO)或 CoWoS封裝中,以實現最終系統整合。

CoWoS 家族,主要針對需要整合先進邏輯和高頻寬存儲器的 HPC 應用。台積公司已經支援超過 25 個客戶的逾 140 種 CoWoS 產品。所有 CoWoS 解決方案的中介層面積均在增加,以便整合更多先進硅芯片和高頻寬存儲器堆棧,以滿足更高的效能需求。台積公司正在开發具有高達 6 個光罩尺寸(約 5,000 平方毫米)重布线層(RDL)中介層的 CoWoS 解決方案,能夠容納 12 個高頻寬存儲器堆棧。

來到InFO 制程技術,在行動應用方面,InFO PoP 自 2016 年开始量產並運用於高階行動裝置,可以在更小的封裝規格中容納更大、更厚的系統單芯片(SoC)。在 HPC 應用方面,無基板的 InFO_M 支援高達 500 平方毫米的小芯片整合,適用於對外型規格敏感度較高的應用。

至於3D 硅堆棧技術, SoIC-P 採用 18-25 微米間距微凸塊堆棧技術,主要針對如行動、物聯網、客戶應用等較爲成本敏感的應用。SoIC-X 採用無凸塊堆棧技術,主要針對 HPC 應用。其芯片對晶圓堆棧方案具有 4.5 至 9 微米的鍵合間距,已在台積公司的 N7 制程技術中量產,運用於HPC 應用。SoIC 堆棧芯片可以進一步整合到 CoWoS、InFo 或傳統覆晶封裝中,運用於客戶的最終產品。

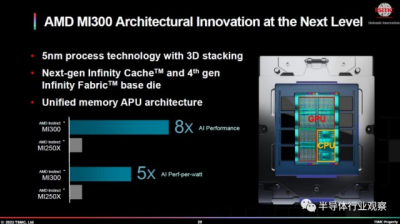

AMD 成功展示了採用 SoIC-X 技術將 N5 GPU 和 CPU 堆棧於底層芯片,並整合在CoWoS 封裝中,以滿足次世代百萬兆級(exa-scale)運算的需求,此爲台積公司的3DFabric 技術如何推動 HPC 創新的具體例子。

特殊制程

台積公司提供了業界最全面的特殊制程產品組合,包括電源管理、射頻、CMOS 影像感測等,涵蓋廣泛的應用領域。

首先看汽車方面,隨着汽車產業朝向自動駕駛發展,運算需求正在快速增加,且需要最先進的邏輯技術。到 2030 年,台積公司預計 90%的汽車將具備先進駕駛輔助系統(ADAS),其中 L1、L2 和 L2+/L3 將有望各達市佔率 30%。

在過去三年,台積公司推出了汽車設計實現平台(ADEP),透過提供領先業界、Grade 1 質量認證的 N7A 和 N5A 來釋放客戶的汽車創新。爲了讓客戶在技術成熟前就能預先進行汽車產品設計,台積公司推出了 Auto Early,作爲提前啓動產品設計並縮短上市時間的墊腳石。N4AE 是基於 N4P 开發的新技術,將允許客戶在 2024 年开始進行風險生產。N3AE 作爲 N3A 的堅實基礎, N3A 將於 2025 年全面通過汽車制程驗證,並將成爲全球最先進的汽車邏輯制程技術。

針對5G 和連網性的先進射頻技術需求,台積公司在 2021 年推出了 N6RF,該技術是基於我們創紀錄的 7 納米邏輯制程技術,在速度和能源效率方面皆具有同級最佳的晶體管效能。結合了出色的射頻效能以及優秀的7納米邏輯速度和能源效率,台積公司的客戶可以藉由從 16FFC 轉換到 N6RF,在半數位和半類比的射頻 SoC 上實現功耗降低 49%,釋放行動裝置的能源預算以支援其他不斷成長的功能。

台積公司日前宣布推出最先進的互補式金屬氧化物半導體(CMOS)射頻技術N4PRF,預計於 2023 年下半年發布。相較於 N6RF,N4PRF 邏輯密度增加 77%,且在相同效能下,功耗降低 45%。N4PRF 也比其前代技術 N6RF 增加了 32%的 MOM 電容密度。

台積電還有超低功率的方案。據介紹,台積公司的超低功率解決方案持續推動降低 Vdd,以實現對電子產品而言至關重要的節能。台積公司不斷提升技術水平,從 55ULP 的最小 Vdd 爲 0.9 伏特,到 N6e 的Vdd 已低於 0.4 伏特,我們提供廣泛的電壓操作範圍,以實現動態電壓調節設計來達成最佳的功率∕效能。相較於 N22 解決方案,即將推出的 N6e 解決方案可提供約 4.9 倍的邏輯密度,並可降低超過 70%的功耗,爲穿戴式裝置提供具吸引力的解決方案。

在MCU / 嵌入式非揮發性存儲器方面,台積公司最先進的 eNVM 技術已經發展到了基於 16/12 納米的鰭式場效晶體管(FinFET)技術,讓客戶得以從 FinFET 晶體管的優秀效能中受益。由於傳統的浮閘式 eNVM 或 ESF3技術越來越復雜,台積公司亦大量投資於 RRAM 和 MRAM 等新的嵌入式存儲器技術。這兩種新技術都已經取得了成果,正在 22 納米和 40 納米上投產。台積公司正在計劃开發 6 納米技術。

來到RRAM,台積電已經於 2022 年第一季开始生產 40/28/22 納米的RRAM。台積公司的 28 納米RRAM 進展順利,具備可靠效能,適於汽車應用。台積公司正在开發下一代的 12 納米RRAM,預計在 2024 年第一季就緒。

太極公司也從2020 年开始生產的 22 納米MRAM 主要用於物聯網應用,現在,台積公司正在與客戶合作將 MRAM 技術應用於未來的汽車應用,並預計在 2023 年第二季取得 Grade 1 汽車等級認證。

至於CMOS 影像感測,雖然智能型手機的相機模塊一直是互補式金屬氧化物半導體(CMOS)影像感測技術的主要驅動力,但台積公司預計車用相機將推動下一波 CMOS 影像傳感器(CIS)成長。爲了滿足未來傳感器的需求,實現更高質量且更具智慧的感測,台積公司一直致力於研究多晶圓堆棧解決方案,以展示新的傳感器架構,例如堆棧像素傳感器、最小體積的全域快門傳感器、基於事件的 RGB 融合傳感器,以及具有整合存儲器的 AI 傳感器。

針對顯示器應用,在 5G、人工智能和 AR/VR 等技術驅動下,台積公司正致力於爲許多新應用提供更高的分辨率和更低的功耗。下一代高階 OLED 面板將需要更多的數位邏輯和靜態隨機存取存儲器(SRAM)內容,以及更快的幀率,爲了滿足此類需求,台積公司正在將其高壓(HV)技術導入到 28 納米的產品世代中,以實現更好的能源效率和更高的靜態隨機存取存儲器密度。台積公司領先的 Display on silicon 技術可以提供高達 10 倍的像素密度,以實現如 AR 和 VR 中使用的近眼顯示器所需之更高分辨率。

產能布局

爲了滿足客戶不斷增長的需求,台積公司加快了晶圓廠拓展的腳步。從 2017 年到 2019 年,台積公司平均每年進行大約 2 期的晶圓廠建設工程。從 2020 年到 2023 年,台積公司晶圓廠的平均建設進度大幅增加至每年約 5期的工程。

在過去兩年,台積公司總共展开了 10 期的晶圓廠新建工程,包括在台灣的5 期晶圓廠工程與 2 期先進封裝廠工程,以及海外的 3 期晶圓廠工程。

28 納米及以下制程的海外產能在 2024 年將比 2020 年成長 3 倍。

在台灣,台積公司 N3 制程量產的基地在南科 18 廠;此外,台積公司正在爲 N2 制程的新晶圓廠進行准備。在美國,台積公司正在亞利桑那州建造 2 期晶圓廠。

公司第一期 N4 晶圓廠已經开始移入設備,並將在 2024 年开始生產。第二期晶圓廠正在興建中,計劃以 N3 制程進行生產。這兩期晶圓廠將合計年產 60 萬片晶圓。

在日本,台積公司正在熊本興建一座晶圓廠,計劃以16/12納米和28納米家族提供晶圓制造服務,以應對全球市場對特殊制程的強烈需求。這座晶圓廠的建設工程已經开始,並將在2024年邁入量產。

台積公司在先進制程的缺陷密度(D0)和每百萬件產品缺陷數(DPPM)方面的領先地位,展現了其制造卓越性。

N5 制程復雜度遠高於 N7,但在相同階段,N5 的良率優化比 N7 更好。

台積公司 N3 制程技術在高度量產中的良率表現領先業界,其 D0 效能已經與 N5 同期的表現相當。

台積公司 N7 和 N5 制程技術在包括智能型手機、計算機和汽車等方面,展現了領先業界的 DPPM,我們相信 N3 的 DPPM 很快就能追上 N5 的表現。

透過利用台積公司領先業界的 3DFabric制造技術,客戶可以克服系統級設計復雜性的挑战,加速產品創新。CoWoS 和 InFO 家族在量產後很快就達到了相當高的良率。SoIC 和先進封裝的整合良率將達到與 CoWoS 和 InFO 家族相同的水平。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電未來,靠這些技術了

地址:https://www.breakthing.com/post/58844.html