來源:內容來自半導體行業觀察綜合,謝謝。

日前,台積電宣布,其先進後端工廠Fab 6 啓用,這是該公司首個一體化自動化先進封裝和測試晶圓廠,以實現前端到後端工藝和測試的 3DFabric 集成服務。該晶圓廠准備量產TSMC-SoIC(集成芯片系統)工藝技術。Advanced Backend Fab 6 使台積電能夠靈活分配產能,用於 TSMC 3DFabric 先進封裝和硅堆疊技術,如 SoIC、InFO、CoWoS 和先進測試,提高生產良率和效率。

Advanced Backend Fab 6於2020年开工建設,支持下一代HPC、AI、移動應用等產品,幫助客戶實現產品成功,贏得市場先機。該晶圓廠位於竹南科學園區,基地面積達14.3公頃,是台積電迄今爲止最大的先進後道晶圓廠,潔淨室面積大於台積電其他先進後道晶圓廠的總和。台積電估計,該晶圓廠將具備年產100萬片以上12吋晶圓等效3DFabric制程技術的能力,以及每年超過1000萬小時的測試服務。

“小芯片堆疊是提高芯片性能和成本效益的關鍵技術。爲響應市場對 3D IC 的強勁需求,台積電已完成先進封裝和硅堆疊技術產能的早期部署,並通過 3DFabric 平台提供技術領先地位。”服務、質量和可靠性。“憑借滿足客戶需求的產能,我們將共同釋放創新,成爲客戶長期信賴的重要合作夥伴。”

台積電利用智能制造來優化晶圓廠的生產效率。工廠內置的五合一智能自動化物料搬運系統全長超過32公裏。從wafer到die,生產信息與敏捷調度系統打通,縮短生產周期。這些系統與人工智能相結合,同時進行精確的過程控制,實時檢測異常,建立強大的芯片級大數據質量防御網絡。每秒的數據處理能力是前端晶圓廠的500倍,通過die traceability構建每個die的完整生產歷史。

台積公司營運/先進封裝技術暨服務、品質暨可靠性副總經理何軍博士表示,「微芯片堆疊是提升芯片效能與成本效益的關鍵技術,因應強勁的三維集成電路(3DIC)市場需求,台積電已完成先進封裝及硅堆疊技術產能的提前部署。」

先進封裝的好處在於,能將記憶體、邏輯和感測等不同功能芯片封在一顆芯片內,客戶可以混合搭配制程,僅在重要的功能上採用3/5納米制程,其余則採成熟制程,不僅提升芯片效能又可降低成本。如今竹南廠的啓用,也是台積電在先進封裝領域的裏程碑,目前如Google自研的TPU(張量處理器)、蘋果M2處理器等都有先進封裝的足跡。

何軍強調,「台積電透過3D Fabric平台提供技術領先與滿足客戶需求的產能,共同實現跨時代的科技創新,成爲客戶長期信賴的重要夥伴」。3D堆疊使得芯片整合密度進一步提升,不僅有更多空間容納新功能芯片,也縮短芯片間訊號傳輸的距離,竹南廠的加入,提供台積電更完備且具彈性的SoIC(系統整合晶片)、InFO(整合扇出型封裝)、CoWoS及先進測試等產能規劃,台積電將如虎添翼。

台積電先進封裝,最新進展

在之前,我們整理了semiwiki早前發布的關於台積電先進工藝的報道(具體查看《台積電工藝的最新分享:信息量巨大》)。近日,他們又更新了關於台積電最新封裝的報道,我們在這裏也分享給大家。

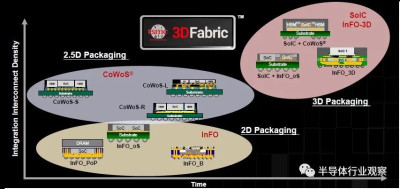

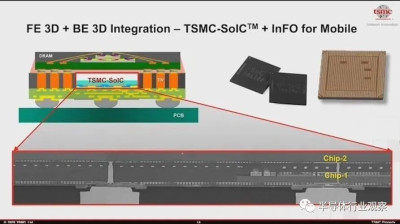

對台積電熟悉的讀者應該知道,晶圓代工巨頭已將其 2.5D 和 3D 封裝產品合並爲一個品牌——“3D Fabric”。按照他們的期望,未來的客戶會同時追求這兩種選擇,以提供系統級功能的密集、異構集成——例如,“前端”3D 垂直組裝與“後端”2.5D 集成相結合。

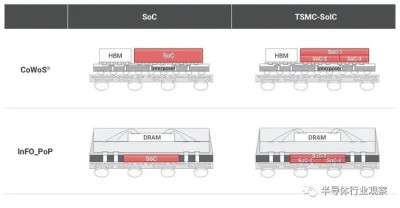

從技術上講,SoC 與“3D”高帶寬內存 HBM 堆棧的 2.5D 集成已經是一種組合產品。如上圖所示,台積電正在設想未來更豐富的拓撲組合,將 3D SoIC 與 2.5D CoWoS/InFO 相結合,作爲非常復雜的異構系統設計的一部分。

與研討會上的工藝技術演示一樣,封裝技術的更新非常簡單——這表明其路线圖的成功、只需要持續執行即可,其中有幾個代表新方向的特定區域我們將在下面突出顯示。

特別值得注意的是台積電對先進系統集成工廠的投資,該工廠將支持 3D Fabric 產品,提供完整的組裝和測試制造能力。按照台積電所說,這座在竹南打造全球首座全自動化 3D Fabric先進封裝廠預計今年下半年开始生產。

爲什么聚焦先進封裝

在大家一貫的理解中,台積電所從事的其實是晶圓代工的業務。但進入新世紀,無論是台積電,還是三星甚至 Intel,都把先進封裝當做公司的一大工作重點,這主要是在日益增長的性能需求與摩爾定律的逐漸失效的矛盾影響下所演進出來的折中結果。

如semiwiki報道所說,對於許多其他應用,摩爾定律不再具有成本效益,尤其是對於集成異構功能而言,多芯片模塊(Multi-chip modules :MCM)和系統級封裝(System in PackageSiP)等“Moore than Moore”技術已成爲將大量邏輯和存儲器,模擬,MEMS等集成到(子系統)解決方案中的替代方案。但是,這些方法仍然是非常特定於客戶的,並且會花費大量的开發時間和成本。

翻看芯片發展的歷史,其實先進封裝這個概念已經存在了數十年。折中通過在封裝中組裝不同且先進的芯片是推進芯片設計的方法之一。今天,這個概念有時被稱爲異構集成。盡管如此,由於成本的原因,高級封裝主要用於高端,面向利基市場的應用。

但這那可能很快就會改變。因爲IC縮放是推進設計的傳統方式,它縮小了每個節點上的不同芯片功能,並將它們封裝到單片式芯片上。但是,IC縮放對許多人來說變得太昂貴了,並且每個節點的收益都在減少。

雖然縮放仍然是新設計的一種選擇,但業界正在尋找替代方案,包括高級封裝。而變化的是,該行業正在开發新的高級封裝類型或擴展現有技術。

高級封裝背後的動機仍然是相同的。與其將所有芯片功能塞在同一個芯片上,不如將它們分解並將它們集成到一個封裝中。據說這可以降低成本並提供更好的產量。另一個目標是使芯片彼此靠近。許多先進分裝使內存更接近處理器,從而以較低的延遲更快地訪問數據。

這聽起來很簡單,但是這裏有幾個挑战。另外,沒有一種可以滿足所有需求的封裝類型。實際上,芯片客戶面臨着各種各樣的選擇。其中:扇出(晶圓級封裝中的集成die和組件)、2.5D / 3D(芯片在封裝中並排放置或彼此疊放)和3D-IC:(在內存上堆疊內存,在邏輯上堆疊或者在邏輯上堆疊邏輯)就成了三種常見的選擇。

此外,業界也正在追求一種稱爲Chiplets的概念,該概念支持2.5D / 3D技術。這個想法是您在庫中有一個模塊化芯片或小芯片的選擇。然後,將它們集成到一個封裝中,並使用die到die的互連方案將它們連接起來。

在台積電方面,爲了滿足市場對新型多芯片IC封裝解決方案的需求,他們也與其OIP合作夥伴合作开發了先進的IC封裝技術,以提供經濟的解決方案,以實現摩爾定律以外的集成。

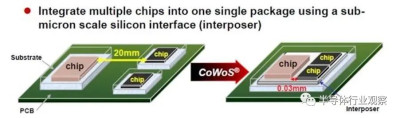

2012年,TSMC與Xilinx一起推出了當時最大的FPGA,它由四個相同的28 nm FPGA芯片並排安裝在硅中介層上。他們還开發了硅通孔(TSV),微凸點和再分布層(re-distribution-layer:RDL),以將這些構件相互連接。台積電基於其構造,將該集成電路封裝解決方案命名爲CoWoS(Chip-on-Wafer-on-Substrate)。這種基於積木和EDA支持的封裝技術已成爲高性能和高功率設計的實際行業標准。

台積電於2017年宣布了InFO(Integrated FanOut technology)技術。它使用polyamide film代替CoWoS中的硅中介層,從而降低了單位成本和封裝高度,這兩項都是移動應用成功的重要標准。台積電已經出貨了海量用於智能手機的InFO設計。

台積電於2019年又推出了集成芯片系統(SoIC)技術。借助前端(晶圓廠)設備,TSMC可以非常精確地對准,然後使用許多窄間距的銅焊盤進行壓焊(compression-bond)設計,以進一步最小化形狀因數,互連電容和功率。

這兩種技術就逐漸演進成了今天的3D Fabric。

2022年的最新更新

如上文所示,按照台積電的規劃,現在他們的封裝技術有2.5D和3D兩種,我們先來看一下他們的2.5D。據介紹,台積電現在有兩類 2.5D 封裝技術——“基片上芯片”(CoWoS:chip-on-wafer-on-substrate) 和“集成扇出”(InFO:integrated fanout)。(請注意,在上圖中,一些 InFO 產品被 TSMC 表示爲“2D”。)

這兩種技術的關鍵舉措是繼續擴大最大封裝尺寸,以便集成更多的die(和 HBM 堆棧)。例如,在硅中介層 (CoWoS-S) 上制造互連層需要“縫合”(stitching)多個光刻曝光——目標是按照最大標线尺寸的倍數來增加中介層尺寸。

首先看CoWoS,據介紹,台積電CoWoS 已擴展到提供三種不同的中介層技術(CoWoS 中的“晶圓”):

1.CoWoS-S:據台積電介紹,在這種封裝模式下,使用硅中介層,基於現有的硅片光刻和再分布層處理

自 2012 年开始批量生產,迄今已爲 20 多個客戶提供超過 100 種產品

中介層集成了嵌入式“溝槽”電容器

开發中的 3 倍最大標线尺寸 – 支持具有 2 個大型 SoC 和 8 個 HBM3 內存堆棧的設計配置,以及 eDTC1100 (1100nF/mm**2)

2.CoWoS-R:在這種封裝模式下,使用有機中介層以降低成本

多達 6 個互連重新分布層,2um/2um L/S

4倍光罩尺寸,支持一個 SoC 和 2 個 HBM2 堆棧,採用 55mmX55mm 封裝;2.1X 光罩尺寸正在开發中,2 個 SoC 和 2HBM2 採用 85mmX85mm 封裝

3.CoWoS-L:使用插入有機中介層的小型硅“橋”,用於相鄰die邊緣之間的高密度互連(0.4um/0.4um L/S 間距)

2X 標线尺寸支持 2 個具有 6 個 HBM2 堆棧的 SoC 2023);

4X 光罩尺寸正在开發中,以支持 12 個 HBM3 堆棧 (2024)

台積電強調,他們正在與 HBM 標准組就 CoWoS 實施的 HBM3 互連要求的物理配置進行合作。(對於堆棧定義,HBM3 標准似乎已經確定了以下內容:4GB 容量(4 個 8Gb 裸片)到 64GB(16 個 32Gb 裸片);1024 位信號接口;高達 819GBps 帶寬。)這些即將推出的 CoWoS 配置具有多個HBM3 堆棧將提供巨大的內存容量和帶寬。

此外,由於預計即將推出的 CoWoS 設計會出現更大的功耗,台積電正在研究合適的冷卻解決方案,包括改進芯片和封裝之間的熱界面材料 (TIM),以及從空氣冷卻過渡到浸沒冷卻。

在介紹完CoWoS之後,我們再看其InFO封裝技術。

據了解,這種封裝技術是在臨時載體上准確(面朝下)放置方向後,將die封裝在環氧樹脂“晶圓”中。再分配互連層被添加到重構的硅片表面。然後封裝凸塊直接連接到再分布層。

按照台積電所說,公司的這個封裝共有 InFO_PoP、InFO_oS 和 InFO_B 幾種拓撲。

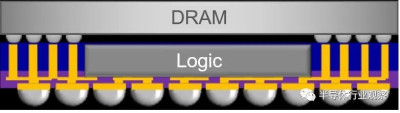

如下圖所示,InFO_PoP 表示封裝上封裝(package-on-package)配置,專注於 DRAM 封裝與基礎邏輯芯片的集成。DRAM 頂部裸片上的凸塊利用 InFO 通孔 (TIV) 到達重新分布層。

台積電表示,InFO_PoP 主要用於移動平台,自 2016 年面試以來,該封裝的芯片出貨量已經超過 12億。按照台積電所說,在當前的InFO_PoP模式下,其 DRAM 封裝是定制設計,因此只能在台積電制造。爲此台積電正在开發另一種 InFO_B 拓撲,在頂部添加現有 (LPDDR) DRAM 封裝,並允許外部合同制造商提供組裝。

InFO_oS (on-substrate) 則可以封裝多個die,再分配層及其微凸塊通過 TSV 連接到基板。

這是一個生產超過 5 年的技術,專注於 HPC 客戶。從技術細節上看,該封裝的基板上有 5 個 RDL 層,具有 2um/2um L/S。這就讓該基板可實現較大的封裝尺寸,目前爲 110 毫米 X 110 毫米。按照台積電所說,公司後續將計劃提供更大尺寸——130um C4凸點間距

至於InFO_M 則是 InFO_oS 的替代品,具有多個封裝die和再分布層,無需額外的基板 + TSV(能實現

在介紹完了台積電的2.5D封裝之後,我們進入他們的3D封裝世界。其中,有一種被稱爲InFO-3D的3D 堆疊封裝技術,該技術利用與再分布層和 TIV 垂直集成的微凸塊芯片,專注於移動平台。

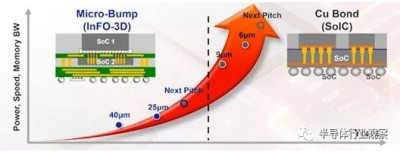

如圖所示,台積電還有一種更先進的垂直die堆疊 3D 拓撲封裝系列——被稱爲“集成芯片系統”(SoIC)。它利用裸片之間的直接銅鍵合,能獲得非常基金的pitch。

按照台積電所說,公司共有兩種 SoIC 產品——“wafer-on-wafer”(WOW)和“chip-on-wafer”(COW)。其中WOW 拓撲在晶圓上集成了一個復雜的 SoC die,提供深溝槽電容器 (DTC) 結構以實現最佳去耦。更通用的 COW 拓撲堆疊多個 SoC die。

適合 SoIC 組裝的工藝技術如下表所示。

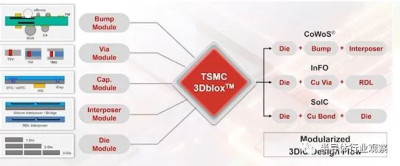

按照台積電所說,公司的3DFabric 的設計支持還包括了3Dblox。如上圖 3D Fabric 圖像的右上角所示,TSMC 正在設想復雜的系統封裝內設計實現,結合 3D SoIC 和 2.5D 技術。

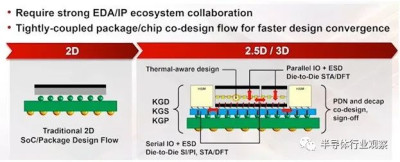

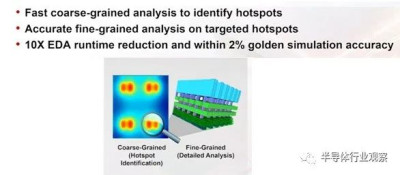

如上所述,這個設計流程非常復雜,需要高級的熱、時序和 SI/PI 分析流程(也可以處理模型數據量)。爲了支持這些系統級設計的开發,台積電與 EDA 供應商就三個主要的設計流程計劃進行了合作:

當中首先包括使用粗粒度加細粒度方法以獲得改進的熱分析。

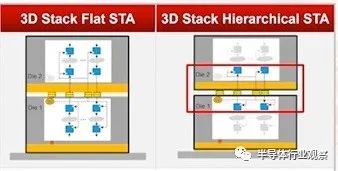

其次,台積電與EDA巨頭還在分層靜態時序分析(hierarchical static timing analysis)上合作。讓單個die由抽象模型表示,以降低總(multi-corne)數據分析的復雜性。

最後,台積電與EDA巨頭還在前端設計分區傻姑娘進行了合作。二爲了幫助加速復雜系統的前端設計劃分,台積電還實施了一項名爲“3Dblox”的計劃。

按照台積電所說,公司這個計劃的目標是將整個物理封裝系統分解爲模塊化組件,然後將其集成。如圖所示,該計劃的模塊類別有:bumps/bonds、vias、caps、interposers和die。

借助該計劃,這些模塊將被整合到任何 SoIC、CoWoS 或 InFO 封裝技術中。

特別值得注意的是,台積電正在努力使 3D Fabric 設計能夠使用各種 EDA 工具——也就是說,使用一種 EDA 供應商工具來完成物理設計,並且(可能)使用不同的 EDA 供應商產品來支持時序分析、信號完整性/電源完整性分析,熱分析。

3Dblox 似乎將 SoC 的“參考流”(reference flows)概念提升到了一個新的水平,台積電推動了 EDA 供應商數據模型和格式之間的互操作性。3Dblox 的整體flow capability將於 2022 年第三季度推出。(初步步驟——即在 InFO 上自動路由再分配信號——將是第一個發布的功能。)

顯然,由於 2.5D 和 3D 配置的預期增長,台積電在先進封裝技術开發和(尤其是)新制造設施方面進行了大量投資。從 HBM2/2e 到 HBM3 內存堆棧的過渡將爲使用 CoWoS 2.5 技術的系統設計帶來可觀的性能優勢。移動平台客戶將擴大 InFO 多芯片設計的多樣性。結合 3D 和 2.5D 技術的復雜 3DFabric 設計的採用無疑也會增加,利用台積電努力“模塊化”設計元素以加速系統分區,以及他們努力啓用廣泛的 EDA tools/flows的應用。

封裝技術基本面

按照台積電方面的定義,諸如CoW(chip-on-wafer)和WoW(wafer-on-wafer)等前 端芯片堆疊技術統稱爲“ SoIC”,即集成芯片系統(System of Integrated Chips)。這些技術的目標是在不使用後端集成選項上看到的“bumps”的情況下,將硅片堆疊在一起。在這裏,SoIC設計實際上是在創建鍵合接口,以便硅可以放在硅的頂部,就好像它是一整塊硅一樣。

根據台積電官方介紹,公司的SoIC服務平台提供創新的前段3D芯片間堆疊技術,用於重新集成從片上系統(SoC)劃分的小芯片。最終的集成芯片在系統性能方面優於原始SoC。它還提供了集成其他系統功能的靈活性。台積電指出,SoIC服務平台可滿足雲,網絡和邊緣應用中不斷增長的計算,帶寬和延遲要求。它支持CoW和WoW方案,而這兩種方案在混合和匹配不同的芯片功能、尺寸和技術節點時提供了出色的設計靈活性。

具體而言,台積電的SoIC技術是將多個die堆疊到“ 3D構造塊”(又稱爲“ 3D Chiplet”)中的一種非常強大的方法。

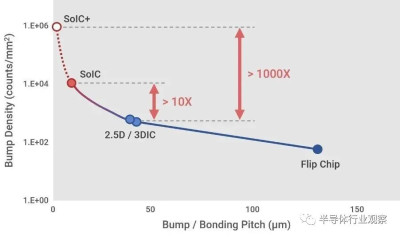

如今,SoIC在垂直堆疊的芯片之間的每平方毫米空間能夠實現約10,000個互連。但看法這正在進行向每平方毫米100萬個互連的开發工作。3D-IC愛好者一直在尋找一種能夠實現這種細微互連,進一步減小外形尺寸,消除帶寬限制,簡化die堆疊中的熱量管理以及將大型、高度並行系統集成到其中的IC封裝方法。

按照台積電所說,SoIC的好處之一體現在在其熱性能。但是,這些SoIC技術的不利之處在於,堆疊設計必須彼此協同設計。然而諸如EMIB之類的微凸點技術以一種技術上可以將一系列芯片連接在一起的方式進行。使用類似COW和WOWO的SoIC技術,則從一开始就固定了設計。

盡管如此,台積電仍熱衷於提高其SoIC芯片堆疊能力。根據台積電的規劃,這是他們面向未來集成的一項關鍵技術,它超越了過去的中介層或芯片堆疊的實現方式,因爲它允許在不使用任何微凸點的情況下堆疊硅芯片,而直接將硅的金屬層對准並鍵合到硅芯片上。

封裝中的另一個相對簡單的方案就是在一個封裝中連接兩個硅芯片。通常,這是通過兩塊硅片並排進行的,並採用多種連接方式。大多數人最熟悉的是中介層方法,該方法將一大塊硅片置於所有互連的die下面,並且比簡單地通過PCB封裝鋪設走线,它的布线方法更快捷。

類似地,另一種方法是將中介層嵌入在PCB中,僅用於將一個特定的die連接到另一個die(這就是Intel稱爲其嵌入式多管芯互連橋或EMIB)。

第三個是die對die的直接垂直堆疊,但是,由於在兩塊硅片之間使用了微凸塊,因此這與上面提到的SoIC實現不同——SoIC使用了鍵合。實際上,台積電下半年產品中的所有實現都是基於微凸塊的,因爲這允許在制造完每個芯片之後更好地混合和匹配不同芯片之間的場景,但是並沒有獲得SoIC提供的密度或功耗優勢。

這就是爲什么它被稱爲“後段”高級封裝的原因。具有HBM功能的GPU就是通過這樣實現的。

許多支持HBM的GPU具有一個GPU裸片,幾個HBM裸片,所有這些裸片都放置在中介層的頂部。GPU和HBM由不同公司制造(甚至可以使用不同的HBM),而硅中介層也可以在其他地方制造。該硅中介層可以是無源的(不包含邏輯,僅僅是die到die間的路由),也可以是有源的,並且如果需要,可以設計爲在芯片之間實現更好的網絡互連,盡管這意味着中介層會消耗電源。

台積電類似GPU中介層的策略在過去一直被稱爲CoWoS(chip-on-wafer-on-substrate)。作爲3DFabric的一部分,從實現方式上劃分,CoWoS現在具有三個變體:

每個人都熟悉的標准稱爲CoWoS-S,其中S代表Silicon Interposer。CoWoS-S的局限性在於中介層的尺寸,該終結通常基於65nm制造工藝或類似工藝制造。由於中介層是單片硅片,因此必須類似地制造,並且隨着我們進入小芯片時代,客戶要求越來越大的中介層,這意味着台積電必須能夠制造它們(並提供高產量) 。

傳統芯片受標线(reticle)的大小限制,這是機器內部的基本限制,即在單個實例上可以“打印”一層的大小。爲了使芯片尺寸爲標片大小的產品成爲可能,TSMC一直在开發多標线大小的插入器技術,以使這些產品更大。基於台積電自己的路线圖,我們預計2023年的CoWoS實施將是標线的四倍左右,每個產品將允許超過3000 平方毫米的有源邏輯硅。

InFO封裝使芯片可以“扇出”,以在 SoC標准平面圖之外增加其他連接。這意味着,雖然芯片邏輯區域可以很小,但芯片要比邏輯電路更大以容納所有必需的引腳輸出連接。台積電提供InFO已經有很多年了,但是在3DFabric的支持下,它現在將提供與封裝內連接有關的不同類型的InFO。

TMSC的封裝技術也可以結合在同一產品中。通過同時實現前端(SoIC)和後端(InFO)封裝,可以制造出新的產品類別。該公司制作了一個這樣的模型:

從表面上看,台積電將在未來幾年爲客戶提供更多的封裝選擇。他們在這方面的主要競爭者似乎是英特爾,後者已經能夠在一些當前產品和某些即將發布的產品中實現其EMIB和Foveros技術。台積電將受益於與更多項目和客戶合作。

*免責聲明:本文由作者原創。文章內容系作者個人觀點,半導體行業觀察轉載僅爲了傳達一種不同的觀點,不代表半導體行業觀察對該觀點贊同或支持,如果有任何異議,歡迎聯系半導體行業觀察。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:台積電新开了一家封測廠

地址:https://www.breakthing.com/post/66463.html