來源:內容編譯自IMEC,謝謝。

幾十年來,NAND-Flash 一直是低成本和大密度數據存儲應用的主要技術。這種非易失性存儲器存在於所有主要的電子終端市場,例如智能手機、服務器、PC、平板電腦和 USB 驅動器。在傳統的計算機內存層次結構中,NAND-Flash 位於離中央處理器 (CPU) 最遠的位置,與靜態隨機存取存儲器 (SRAM) 和動態 RAM(動態隨機存取存儲器)相比,它相對便宜、速度慢且密集。

閃存領域的重要性體現在其在全球半導體資本支出(capex) 中的可觀份額,數據顯示,其約佔了整個半導體市場支出的三分之一。它的成功與其不斷擴展存儲密度和成本的能力有關——這是 NAND 閃存技術發展的主要驅動力。大約每兩年,NAND-Flash 行業就能夠大幅提高位存儲密度,以增加 Gbit/mm 2表示。

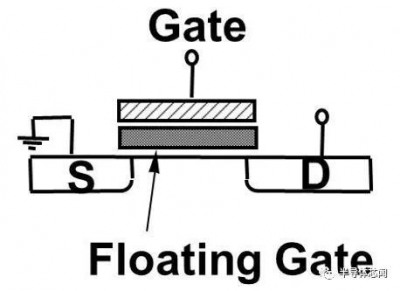

在此過程中,行業也已經引入了多項技術創新來保持這一趨勢线。直到最近,NAND 閃存單元都以平面配置排列,使用浮柵晶體管爲他們的記憶操作。浮柵晶體管由兩個柵極組成:浮柵和控制柵。浮柵與晶體管結構的其余部分隔離,通常由多晶硅制成。控制門是“普通”晶體管門。存儲單元的寫入是通過向控制柵極施加脈衝來完成的,該脈衝基於隧道機制迫使電子進入(或離开)浮柵。電荷的存在(或不存在)會改變晶體管的閾值電壓,這種變化稱爲內存窗口(memory window)。因此,信息被編碼在浮柵晶體管的閾值電壓中,並通過測量漏極電流來完成讀取。存儲在隔離柵極中的電荷長時間保持不變,使存儲器具有非易失性特性。

圖 1:浮柵單元的示意圖。

20 多年來,浮柵一直是 2D-NAND 的常用方法,盡管其結構相當復雜,但仍可提供可靠的操作。通過減小浮柵單元的尺寸,可以提高位存儲密度。然而,2D-NAND 縮放在大約 15nm 半間距處(half pitch)飽和,主要是因爲陣列可靠性和靜電幹擾問題 。

走向 3D 以降低每比特成本

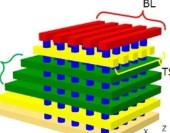

位存儲密度的進一步增加是通過向三維過渡——而不是通過堆疊類似 2D-NAND 的層來實現的,因爲這樣做所需的工藝步驟數量會大大增加成本。“真正的” 3D-NAND背後的基本思想是堆疊單元以形成垂直串,從而達到更高的單位面積密度。在這種配置中,單元仍然由水平字线尋址。

最常見的制造方法,即環柵 (GAA) 垂直溝道方法,從生長氧化物/(犧牲)氮化物(字线)層堆疊开始。接下來,使用先進的幹法蝕刻工具通過堆疊向下鑽取圓柱形孔。沿孔的側壁沉積隧道和俘獲層。爲了完成這個“punch和plug”的過程,在孔內沉積一個薄的多晶硅通道,然後是一個核心填充物,形成一個類似通心粉的結構。在下一步中,去除氮化物並用字线金屬代替。在這些 GAA 結構中,圓柱形柵極環繞通道結構,這增強了載流子注入捕獲層的能力——從而擴大了編程/擦除窗口。

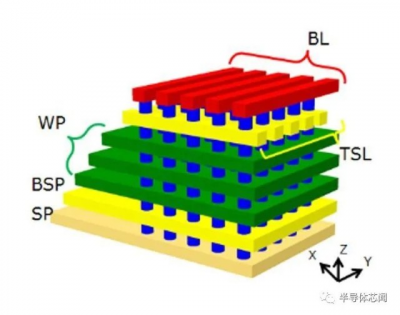

圖 2:典型 的3D-NAND-Flash 結構的表示(BL=bit line; WP=word plate; BSP=bottom select plate; SP=source plate; TSL=top select line)。

通過添加更多層而不是縮小特徵尺寸,NAND-Flash 行業放棄了傳統的縮放方式。第一個商用 3D-NAND 產品於 2013 年推出,堆棧數爲 24 個字线層 (128Gb)。根據供應商的不同,存在結構上的變化,以不同的名稱(例如 V-NAND 和 BICS)而聞名。因此,3D-NAND 是第一個也是(迄今爲止)唯一將真正的 3D 產品推向市場的技術。在接下來的幾年中,爲了保持位密度縮放趨勢线,供應商已經將更多的層疊加在一起。最近,一些主要廠商推出了基於 176 層 3D-NAND 的產品,預計這種增加層數的趨勢將在未來幾年持續下去。

在此過程中,已經實施了額外的創新,以促進具有挑战性的 3D 工藝或允許進一步增加位密度。後者的一個例子是每個單元增加多達4 位的數量,這是 NAND 閃存技術的真正資產。例如,對於 4 位,多電平單元在每個單獨的晶體管中使用 16 個離散電荷電平,這由足夠大的內存窗口啓用。

另一個值得注意的創新是用電荷陷阱單元( charge trap cell)代替浮柵單元,這涉及更簡化的工藝流程。兩種電池類型的工作原理相對相似,但在電荷捕獲電池中,捕獲層是絕緣體——通常是氮化硅——它在相鄰電池之間提供的靜電幹擾較小。這個電荷陷阱單元現在是大多數 3D-NAND 結構的基礎。

提高位存儲密度

爲了維持 NAND-Flash 路线圖,一些主要廠商最近宣布將層數進一步增加到 500 層或更多。按照趨勢线,這個數字將在未來十年內增加到 1,000。增加層數會帶來更高的處理復雜性,它會挑战沉積和蝕刻工藝,並導致應力在層內積聚。爲了應對其中的一些挑战,NAND-Flash 制造商最近开始將層數分成兩(或更多)層,並將單獨處理的層堆疊在一起。

然而,人們越來越擔心如果沒有重大創新,這種演變將逐漸降低 NAND-Flash 存儲產品的成本效率。層數的增加需要對高度先進的沉積和蝕刻工具進行投資。堆疊多層的趨勢將顯着增加掩模數量,以及處理步驟和時間的數量。它還可能導致存儲路线圖放緩,直到 2030 年 1,000 層的堆棧才可用。

隨着層數的增加,由於圖案化和應力原因,存在縮小層厚度和控制堆疊高度的壓力。這種z 間距縮放涉及降低堆疊中涉及的所有材料的高度,包括字线金屬和氧化物,每種材料都會帶來特定的挑战。

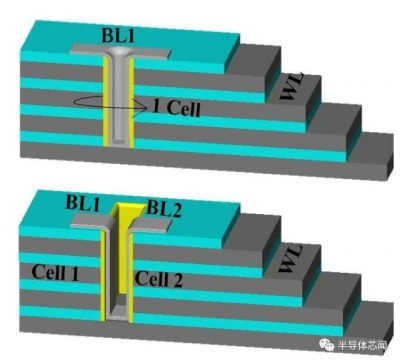

Z-pitch 縮放也可能通過 xy 尺寸的進一步減小來補充。這將需要對存儲單元進行重大創新,而在 3D-NAND 开發的這些年中,這種創新一直保持不變。因此,行業正在探索新材料和單元架構作爲當今 GAA NAND 閃存單元的替代品。一個值得注意的發展是溝槽式架構連接晶體管。

在這種架構中,存儲單元不再是圓形的。它們是在溝槽的側壁上實現的,在溝槽的兩端有兩個晶體管,這顯著增加了位密度。從操作的角度來看,與圓形 GAA NAND-Flash 單元相比,此溝槽單元類似於平面單元單元(直立放置)。雖然它在電氣特性(例如編程/擦除窗口)方面有輕微的損失,但與“GAA”單元相比,溝槽狀配置中的單位單元面積在 xy 方向上可以減小。因此,溝槽單元被提出作爲下一代 NAND-Flash 單元架構——有望將 xy 間距從今天的 140nm(有效)減小到約 30nm。

圖 3:(頂部)Gate-all-around 與(底部)溝槽 NAND-Flash 單元架構。

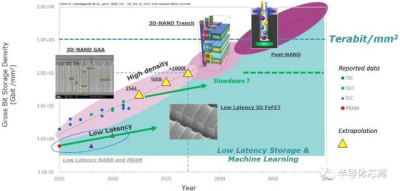

在更遙遠的未來,我們預計將需要更多顛覆性的“後 NAND”創新(例如 imec 的基於液體的概念)來延續密度縮放趨勢並進入太比特/mm 2時代。

憑借在 2D 和 3D-NAND-Flash 技術开發方面的長期記錄,imec 的部分存儲研發活動專注於繼續傳統的 GAA 3D-NAND-Flash 擴展路线圖。通過建模和實驗,該團隊探索了基本 3D-NAND 單元的創新,以進一步減小 xyz 尺寸。通過建模和仿真工作,他們研究了引入新材料和架構對 NAND 閃存單元的電氣性能的影響。建模還使團隊能夠增強基本理解,並識別和緩解 3D-NAND-Flash 單元擴展障礙。實驗工作圍繞具有有限層數的測試車輛構建(通常爲 3 到 5 個,高度 300nm),與研究縮放對電存儲單元指標的影響有關。

對最近的見解和成就的看法

NAND-Flash 層堆棧的 z-shrink 涉及擠壓用於創建字线層的材料,包括字线金屬。目前,商用 3D-NAND 產品中的垂直字线間距介於 50 到 60 納米之間,鎢 (W) 是首選的字线金屬。它還充當 NAND 閃存單元的柵電極,並通過替代金屬柵極工藝集成在堆棧中。減小字线金屬厚度會帶來不必要的電阻率增加,這會增加電阻-電容 (RC) 延遲並減慢存取時間。

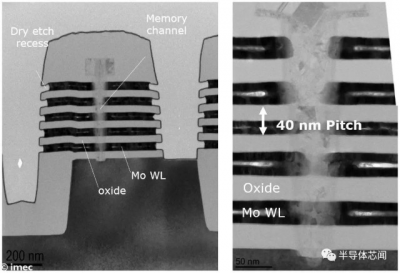

因此,Imec 正在尋找替代金屬例如Ru和(barrierless)Mo,在小尺寸下可能具有較低的電阻率。在 2021 年 IEEE VLSI 技術和電路研討會 (VLSI 2021) 上,該團隊展示了將 Ru 和 Mo 字线的電阻率和存儲特性提高到創紀錄的40nm 字线間距。

圖 4:集成在 5 層 3D-NAND 中的 Mo 的 TEM 橫截面,字线按比例縮小至 40nm 間距。

該團隊還在探索電荷陷阱層、隧道電介質和金屬柵疊層的替代材料,並正在研究它們對存儲器性能的影響。例如,他們研究了高功函數金屬與薄的高 k 襯墊相結合如何改善 3D-NAND 擦除操作。

在當今的 GAA 3D-NAND-Flash 結構中,通道材料使用的是多晶硅。將多晶硅材料沉積在貫穿材料疊層的“plug”中被認爲是制造器件的最具成本效益的方法。但隨着層數的增加,固有缺陷豐富的多晶硅通道會降低器件的讀取電流。

因此,Imec 探索了通過引入替代通道材料或提高多晶硅通道質量來提高通道遷移率的方法。在 2021 年 IEEE 國際電子器件會議 (IEDM 2021) 上,該團隊展示了在 3D 測試結構中使用金屬誘導橫向結晶 (MILC) 來提高多晶硅通道質量的結果。MILC 是一個過程,在該過程中,非晶硅在相對較低的溫度下轉變爲晶態,由鎳等金屬的存在催化。

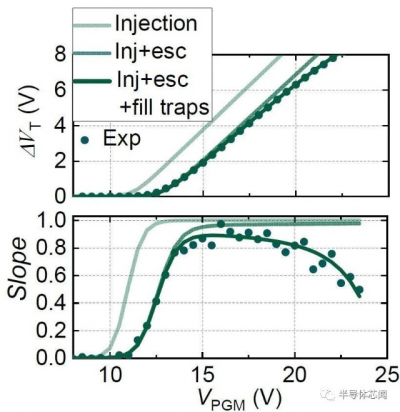

例如,建模工作的重點是了解電荷陷阱層閃存的非理想編程效率。這種低效率反映在增量步進脈衝編程 (ISPP) 曲线的斜率中,導致所需的編程電壓更高。該團隊最近對這種鮮爲人知的現象有了更好的了解。

在 IEDM 2021 上,研究人員概述了對 ISPP 斜率的不同貢獻,並提出了緩解方法,例如,通過在電荷陷阱層單元內使用高 k 電介質。

圖 5:載流子注入 (inj)、逃逸 (esc) 因素和陷阱填充對 ISPP 曲线(頂部)和斜率(底部)的貢獻 。

其他建模工作側重於引入新材料和架構(例如溝槽單元)對層堆疊內的機械應力的影響。衆所周知,機械應力會在 3D-NAND-Flash 結構中引入晶圓翹曲、局部圖案變形和裂縫。在 2021 年 IEEE 國際互連技術會議 (IITC 2021) 上,imec 提出了一種有限元建模 (FEM) 方法,該方法可用於評估和減輕未來 3D-NAND 存儲器制造中的晶圓翹曲,而無需通過實驗構建 >100層堆棧。

如今,3D-NAND-Flash 技術用於高密度、低成本的數據密集型存儲應用,例如固態驅動器。但該技術正越來越多地進入其他細分市場,尤其是低延遲存儲領域。在這裏,它可以潛在地服務於需要比傳統 NAND 閃存更快的讀取訪問時間的一系列存儲應用程序,例如數據庫查找表等應用程序。這種更快的 NAND-Flash 變體將進入存儲類內存 (SCM) 空間,這將有助於縮小快速、易失性 DRAM 和慢速、非易失性 3D-NAND-Flash 之間的差距。

與傳統的高密度 3D-NAND-Flash 相比,低延遲存儲應用需要更短的讀取訪問時間。有幾條路线可以使這成爲可能。一種方法是恢復爲單位存儲單元。這主要將程序速度(~30us)提高到接近讀取速度(~10us)。設計空間的進一步優化可能涉及減少字线長度或改變 RC 延遲參數。通過這些措施和其他措施,NAND-Flash 技術有望以10s 左右的讀取訪問時間進入低延遲存儲市場。

低延遲存儲:FeFET 的主要作用

從長遠來看,鐵電存儲器有望發揮這一作用——尤其是基於3D 鐵電場效應晶體管(3D-FeFET) 的存儲器。預計 3D-FeFET 在速度方面將優於 3D-NAND-Flash,使其成爲低延遲存儲的理想選擇。

圖 6:數據存儲路线圖上的 imec 視圖。

eFET 的架構類似於傳統的 n 溝道 MOS 晶體管,其中柵極電介質已被鐵電材料(例如正交晶相的 HfO 2 )取代。鐵電體可以處於兩種電極化狀態,這可以通過向晶體管柵極施加脈衝來提供的外部電場反轉。去除場後,它們保持其極化狀態,使材料具有非易失性特性。柵極絕緣體的兩個穩定的剩余極化狀態會改變晶體管的閾值電壓。二進制狀態因此被編碼在晶體管的閾值電壓中。FeFET的工作原理內存與 NAND-Flash 非常相似:通過向晶體管柵極施加脈衝來完成對存儲單元的寫入,通過測量漏極電流來執行讀取。

就像 NAND-Flash 一樣,FeFET 可以通過使用類似 3D-NAND 的制造流程以真正的 3D 方式制造 。爲了構建3D-FeFET,類溝槽結構優於 GAA 結構,因爲 FeFET 不會受益於圓形電荷載流子注入。

盡管仍處於研發的早期階段,但與 3D-NAND 相比,3D-FeFET 有望呈現出一些顯着的優勢。它們更易於處理,消耗更少的功率,並且可以在更低的電壓下運行,這有利於它們的可靠性。此外,幾微秒級的讀寫訪問時間是可行的,這使得它們成爲未來低延遲應用的 3D-NAND 的有吸引力的替代品。

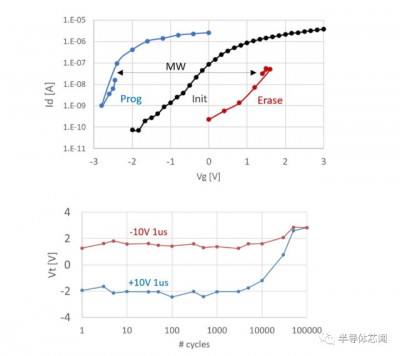

Imec 正在解決與 3D-FeFET 的加工、表徵和可靠性相關的主要挑战。研究人員正在探索可能的最佳架構、材料組合和內存操作方案(例如編程/擦除方案),以優化低延遲存儲應用的 3D-FeFET。要進入 SCM 空間(的 NAND 端),速度和循環耐久性(或失敗前的編程/擦除循環數)是最關鍵的參數。雖然 3D-NAND 的循環壽命限制在 10 5左右,但該團隊正在努力實現 3D-FeFET 的 10 7循環壽命。這已經可以在平面 FeFET 架構中得到證明。預計更高的循環耐久性會伴隨着密度和保持力的輕微損失。

改善循環和速度的一種方法是優化通道材料。就像在 NAND 中一樣,今天的 FeFET 通道是由多晶硅組成的。但這種材料對 FeFET 的操作提出了挑战。與鐵電 HfO 2的結合會刺激界面氧化層的再生長,從而對電荷載流子產生不希望的俘獲效應,並降低存儲器的編程/擦除循環性能。除了研究緩解策略外,imec 還探索了替代通道材料,包括氧化物半導體。這些通道材料應具有低熱預算以保持 HfO 2(或其他鐵電層)的正交相。

圖 7:(頂部)應用 100ns 編程/擦除脈衝後的存儲器窗口;(底部)在編程和擦除之後隨着循環的閾值電壓 VT 的演變。

HfO 2的斜方晶相可以通過使用摻雜劑、應變和退火的最佳組合來穩定。今天,主要使用 Si 作爲摻雜原子,因爲即使在更高的熱預算下它也可以保持正交相。imec 團隊還研究替代摻雜劑和摻雜條件,並探索除 HfO 2之外的其他鐵電材料。

對於架構,imec 積極追求3D 溝槽架構,已經展示了第一個測試設備。

總結

雖然幾十年來NAND-Flash主要針對高密度存儲應用,但我們現在也看到了該技術的更快變體——針對低延遲存儲。對於後一種應用,imec 認爲3D-FeFET在未來將發揮重要作用。對於 NAND 和 FeFET,imec 探索新材料和單元架構,並研究它們對內存性能的影響。此外,該團隊正在更深入地了解主要的可靠性下降機制。雖然 3D-NAND-Flash 的創新旨在延續高密度存儲路线圖,但 imec 爲 3D-FeFET 爲其未來在低延遲存儲市場中的角色做好准備。

本文作者可以追加內容哦 !

鄭重聲明:本文版權歸原作者所有,轉載文章僅為傳播信息之目的,不構成任何投資建議,如有侵權行為,請第一時間聯絡我們修改或刪除,多謝。

標題:NANDFlash何去何從?3DFeFET將擔當重任!

地址:https://www.breakthing.com/post/8259.html